主题中讨论的其他器件:DAC3152、 TRF370417、 DAC3174、TRF3705

很遗憾、我无法在 DAC31x1和 DAC31x4中找到任何原理图(这些都是引脚兼容的)。 此外、EVM 板没有任何原理图。 如果您将这些内容与您的设计布局一起发送给我、我将不胜感激、这样我就能够根据约束条件自行确定方向。 数据表中缺少一些信息、我在此要说明:

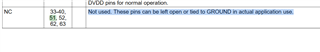

DACCLK 为 LVPECL (对于共模电压为2V、但在数据表中称为0.5V?)、 但在另一个数据表(DAC3152、第17/32页)中、您提到了 DACCLK 引脚是内部偏置的、并且"虽然由于信号摆幅受限而不是最优、但 LVDS 源也可用于驱动时钟输入"、但我不确定这是否适用于 DAC3154? LVDS 的 VDIFF 为400mV、所以这勉强是 DACCLK 能够达到的最小值。 这是可靠的时钟配置吗? 只有交流耦合作用不大、但您的内部偏置可能有用?

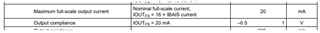

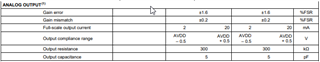

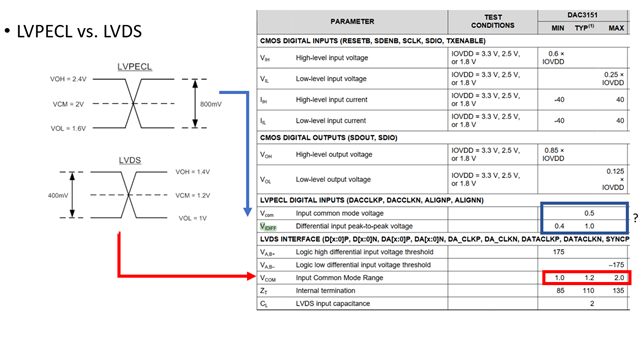

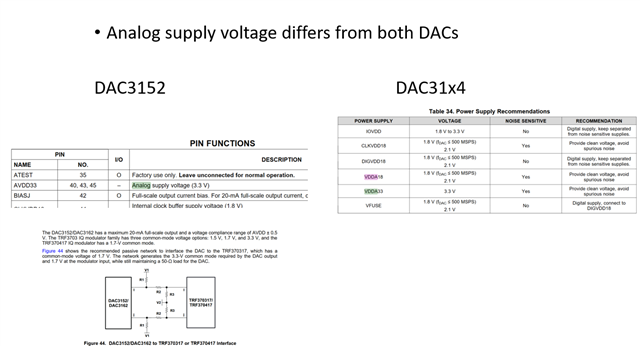

2.我想使用(正如在 DAC3152提到的)调制器 TRF370417、然后我必须匹配两种共模(DAC 输出共模为 AVDD +/- 0.5V)和调制器1.7V。 对于 DAC3154、我们有两个不同的模拟电源电压(AVDD18和 AVDD33)、因此我们应考虑输出共模电压(此问题中已讨论过: https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/462985/dac3152-output-level-low)

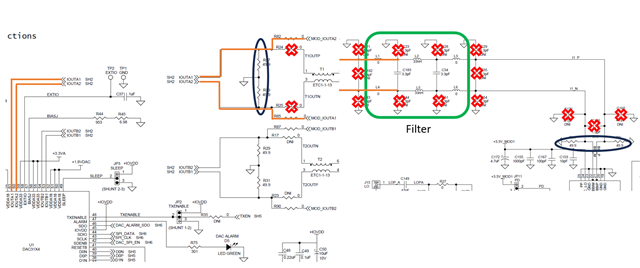

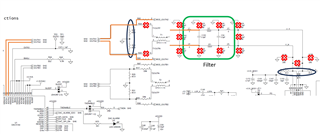

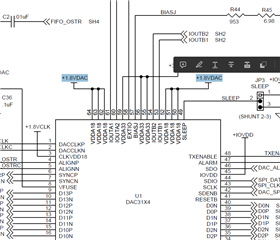

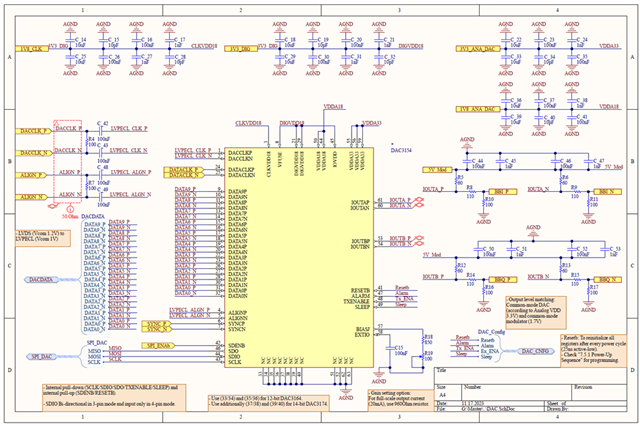

这是我关于 DAC3154的初始原理图、但我仍需要了解这两个不确定性:

非常感谢任何帮助!