AFE5832工程师:

我最近在调试 AFE5832芯片时遇到了两个问题。

问题1:TX_TRIG 信号似乎无效、因为我使用 AFE 芯片接收32个信号、前16通道信号和后16通道信号无法同步、它们具有固定的失准。 为了确保 TX_TRIG 信号有效、我应该怎么做?

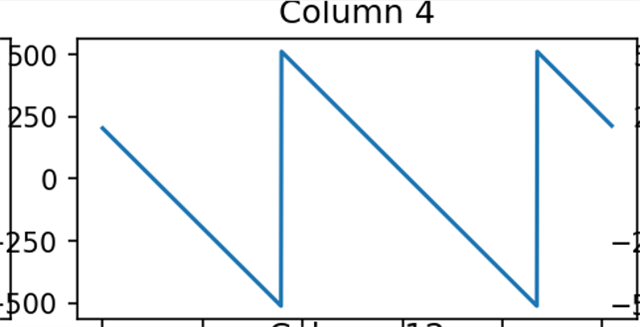

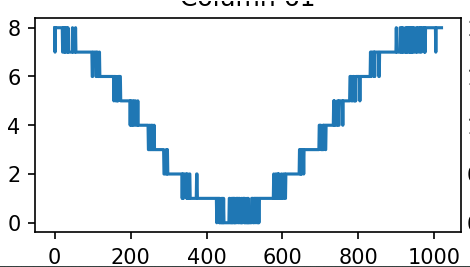

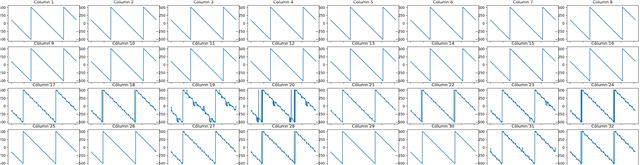

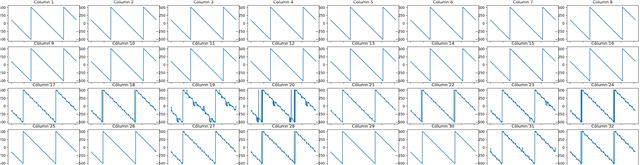

问题2:下图是 AFE5832的斜坡测试模式、但是接收到的通道数据有一些问题、但是有些通道完全正确、我找不到原因。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

AFE5832工程师:

我最近在调试 AFE5832芯片时遇到了两个问题。

问题1:TX_TRIG 信号似乎无效、因为我使用 AFE 芯片接收32个信号、前16通道信号和后16通道信号无法同步、它们具有固定的失准。 为了确保 TX_TRIG 信号有效、我应该怎么做?

问题2:下图是 AFE5832的斜坡测试模式、但是接收到的通道数据有一些问题、但是有些通道完全正确、我找不到原因。

您好!

LVDS 数据被锁存在 DCLK 信号上。 因此、理想情况下、来自 LVDS 数据通道的数据应在 DCLK 中间切换。 如果情况并非如此、则可能存在设置/保持问题、并可能导致时序故障。 在 FPGA 中、您可能有多个 DCLK 相位。 您可以尝试更改显示异常斜坡数据的通道的相位、看看这是否有帮助。

任何与 TX_TRIG 相关的问题都会导致器件之间的同步相关问题。 由于此处一些通道仅显示问题、因此它与 TX_TRIG 不相关。

谢谢!

此致、

沙比尔

我理解了上述问题。 很抱歉、我还有另一个问题。

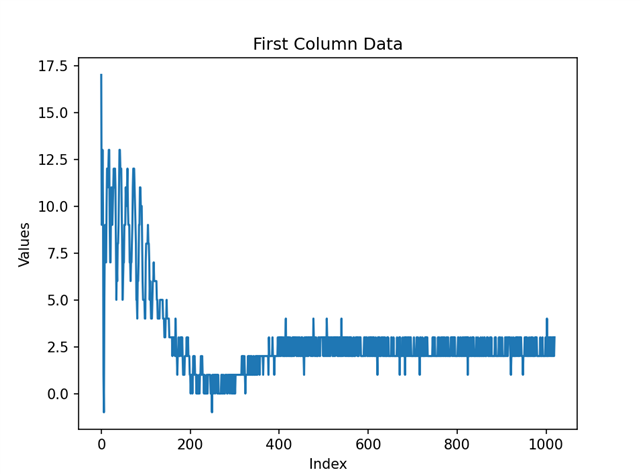

使用测试模式斜坡时、可以观察到主机上接收到的数据值从0增加到511。 然而、当我使用信号发生器来生成一个5mhz 100mvpp 正弦信号输入时、接收到的信号的振幅仅约为0-10。 如果未添加输入信号、则接收到的回波仅为0-15。 这些 AD 样本太小、远小于512。

请问原因是什么? 我已经调整了 LNA PGA 的增益大小、但仍然没有解决这个问题、下面三张图片说明了这个问题。 期待您的回复!