大家好!

我正在研究 DAC11001A 的输出电压稳定时间参数。 然而、只提供了典型时间、我想知道是否有任何数据可用于基于数据表中规定的输入条件的器件最小/最大稳定时间。

谢谢!

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Filipe:

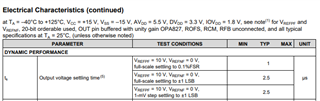

我们实际上并没有最小值/最大值数据、因为这在很大程度上取决于外部放大器、外部负载以及 DAC11001A 中的跟踪保持电路的某些设置。 完全无缓冲且无输出负载、无论电压步长如何、稳定时间都将小于1us。 但是、这将是一个非常有用的配置、我认为您应该查看您想要使用的输出缓冲器、并评估其稳定时间规格。 DAC 的输出阻抗为~6.25k Ω、并且引脚上会有一些寄生电容、因此会稍微减慢瞬态速度。 否则、我们的跟踪和保持电路延迟小于1us。

您好、Paul、

谢谢 您告诉我。 同样、您是否知道、如果按照数据表第8.4.1节中的说明将 FSET 位设置为0、可以改善多少稳定时间? 或者这是否取决于外部因素?

DACx1001 R2R 梯形电路和抗尖峰脉冲电路可以降低波形生成应用中的谐波失真。 快速稳定位(FSET、位10、地址02h)缺省情况下被设定为1、这样 DAC 被配置用于增强的 THD 性能。 可通过使用 SPI 写入将 FSET 位复位为0以启用快速趋稳模式。 在此模式下、可以使用 TNH_MASK (位19:18、地址02h)来配置 DAC 抗尖峰脉冲器电路。 这些位为表7中指定的代码变化禁用抗尖峰脉冲电路。 只有当 FSET = 0 (启用快速趋稳)且 DIS_TNH = 0 (启用抗尖峰脉冲电路)时、这些位才可写入。

尊敬的 Filipe:

FSET=0模式意味着当代码阶跃大于 TNH_MASK 设定的限值时 TnH 被禁用。 我们的想法是、当输出的代码步长较大时、由于输出在写入下一个代码之前未趋稳而引起的 THD 干扰的影响、其重要性低于任何 THD。 UP_RATE 字段设置 TnH 默认时间、通常约为~100-700ns。 它假设我们具有恒定的 采样率。

我认为、优化应用设置的最佳方法是确定给定更新速率和输出音调对应的最大代码步长。 如果您在 TNH_MASK 设置范围内看到代码步骤、则应实现 FSET 函数。