主题中讨论的其他器件:DAC3283

您好!

1. DAC 3283数据表显示:

此处显示最大输入数据速率为312.5MSPS。 这意味着 Max。 DATACLK 频率 可以是312.5 MHz。

但测试条件显示 DATACLK 频率为625MHz。 那么最大值是多少。 DATACLK 频率? (我在此假设 DATACLK 频率与为 DAC 生成的8位数据所在的时钟相同)。

DATACLK 频率应该是 DACCLK 频率的一半吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

1. DAC 3283数据表显示:

此处显示最大输入数据速率为312.5MSPS。 这意味着 Max。 DATACLK 频率 可以是312.5 MHz。

但测试条件显示 DATACLK 频率为625MHz。 那么最大值是多少。 DATACLK 频率? (我在此假设 DATACLK 频率与为 DAC 生成的8位数据所在的时钟相同)。

DATACLK 频率应该是 DACCLK 频率的一半吗?

您好!

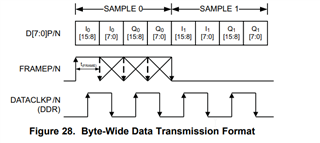

DAC3283是一个字节宽的 DDR 接口。 从下图中可以看出、I/Q 样本每完成一次、需要2个 DATACLK 周期。 I/Q 速率为312.5MSPS 时、这表示 DATACLK 的625MHz。

DATACLK 与 DACCLK 的关系取决于您所选择的插值。 详细信息请见下面。

e2e.ti.com/.../3718.DAC3282_2D00_3-Byte-Wide-DDR-Clocking.pdf

你好, 康夏

感谢您的快速回复。 这对理解事物有很大帮助。

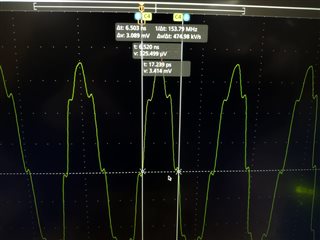

因此、我们的 DATACLK= 307.2 MHz、如果我们生成一个方波信号、我们就能够以高电平时间~ 6.5ns (即半周期= 1/(2xDATACLK)生成它。 如下图所示:

FPGA 逻辑类似于:

始终@(Posedge fpga_clk_mmcm) begin

if (reset) begin (复位)

计数<= 2'b00;

数据<= 8'h00;

结束

如果(count =2'b00)开始、则执行其他操作

数据<=8'h7F;

count = count + 1;

结束

如果(count =2'b10)开始、则执行其他操作

数据<=8'h80;

count = count + 1;

结束

否则 count = count+1;

结束

但如果我们尝试生成高电平时间~ 3.25ns (半周期= 1/DATACLK)的方波信号。 则 DAC 没有输出。

是因为 DAC 需要至少2个 DATACLK 周期来生成输出吗?

我们的要求是生成高电平时间~ 4ns 的方波信号。

但如果我们尝试生成高电平时间~ 3.25ns (半周期= 1/DATACLK)的方波信号。 则 DAC 没有输出。

是因为 DAC 需要至少2个 DATACLK 周期来生成输出吗?

我们的要求是生成高电平时间~ 4ns 的方波信号。

[/报价]是的。 在3.25ns 高电平时间下、这相当于312.5MSPS、接近最大输入数据速率。 在输入数据速率端、本质上会混叠回直流。