主题中讨论的其他器件: TPS7A91、 ADS1278

大家好、

我想了解有关 ADS1274的更多信息。 按照以下顺序执行 Ic 上电序列:DVDD->IOVDD->AVDD。前两个是 IC DVDD (1.8V)、GND 短路;第三个是 IC AVDD (5V)、GND 短路。

是否 需要将无源器件连接到电力线?

谢谢。此致、

阿拉文德

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我想了解有关 ADS1274的更多信息。 按照以下顺序执行 Ic 上电序列:DVDD->IOVDD->AVDD。前两个是 IC DVDD (1.8V)、GND 短路;第三个是 IC AVDD (5V)、GND 短路。

是否 需要将无源器件连接到电力线?

谢谢。此致、

阿拉文德

您好 Aravind:

正确的加电复位需要一个指定的加电顺序。 但是、只要在所有电源稳定后发出/SYNC 脉冲、就无需遵循上电序列。

为了实现一致的性能、当数据首次出现时、在器件上电后置位/SYNC。

一些客户会增加一个与 AVDD 电源串联的铁氧体磁芯。 但是、这不是必需的。 我们强烈建议使用低噪声、高 PSRR 线性稳压器为 AVDD 和 DVDD 电源提供电源、从而获得出色的整体性能。 我们在评估板上使用 TPS7A4700以获得最佳性能、但有很多较低成本的选件、例如 TPS7A91。

此致、

N·基思

精密 ADC 应用

大家好、

上电顺序按照以下顺序:一个 双通道电源中的 DVDD(1.8V)->IOVDD(3.3V),一个单通道电源中的 AVDD 和另一个通道中的 REFP(+2.5V)和 REFN。

在首次 没有热量 issue.second 时间 AVDD (+5V)电流下降.

出现了什么问题?

而 FCLk 引脚输入(PK-PK)电压的 PWM 生成(20MHz)电压为3.3伏。

但20MHz 时钟源通过 DRDY 引脚和 SYNC 引脚

为什么 Fclk 在蔓延?

请给我一个参考...!

谢谢。此致、

阿拉文德有限公司

您好 Aravind:

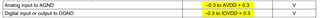

在上电期间、任何输入都不能超过电源电压、这一点很重要。 对于模拟输入和基准输入、这些引脚的电压不能大于 AVDD+/-0.3V 电源、包括在加电期间。 基准输入应在 AVDD 之后上电。 AVDD (+5V)->VREF (+2.5V)。

此外、这同样的限制也适用于数字输入引脚和 IOVDD。 在加电过程中或加电后、任何大于 IOVDD+/-0.3V 的数字引脚上都不应有任何电压。

当器件配置为帧同步模式时、DRDY/FCLK 是输出引脚、由格式引脚决定、并且频率应等于输出数据速率。

CLK 引脚是一个输入引脚、应具有100kHz 到37MHz 范围内的时钟频率、具体取决于所需的最大输出数据速率。 要实现144ksps 的最大数据速率、必须使用帧同步模式、并且 CLK 输入频率应为37MHz。

此致、

基思

大家好、

在此 ADS1274中、上电序列是 DVDD (1.8V)->IOVDD (3.3V)->AVDD (5V)->REFP (2.5V)->FCLK (20MHz)。 我将给出此顺序、但有时上电 正常、但随后 IC 中出现过热。

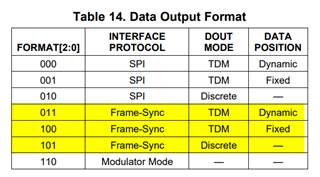

我仅使用 SPI 协议

数据模式-> TDM

数据位置->动态

我将 生成 PWM 输出(20MHz)、直到 clk 输入引脚 Pk-Pk 电压为3.3V。这不受支持吗?

为什么鸡巴传播?

此致、

阿拉文德

您好 Aravind:

ADS1274电源可以按任何顺序加电、包括同步加电、并且不会损坏器件。 但是、如果未遵循数据表上电顺序、则器件在上电期间可能无法正确复位。 在这种情况下、建议在所有电源稳定至建议的工作电压电平后将/SYNC 引脚置为有效。

您提到过、器件在经过某些上电周期后会变烫。 如果在加电期间施加高于 AVDD+0.3V 或 IOVDD+0.3V 的电压、则可能会导致器件故障。 此外、我建议您在加电期间使用示波器来监控电源电压、以确保没有电源过冲并且超过器件的绝对最大额定电压。 如果 IOVDD 瞬间超过3.6V 或 AVDD 超过6V、那么这可能导致器件锁存、不能正常工作、并且由于从电源汲取的过多电流而变得很热。

DRDY 引脚将不等于 CLK 引脚上的频率。 DRDY 将等于数据速率频率。

我将 生成 PWM 输出(20MHz)、直到 clk 输入引脚 Pk-Pk 电压为3.3V。这不受支持吗?

当 IOVDD=3.3V 时、CLK 输入电压也应为3.3V 逻辑电平。 是的、这种情况下受支持。

为什么鸡巴传播?

/DRDY 频率将等于输出数据速率、具体取决于速度和 CLKDIV 引脚设置。 例如、当 CLKDIV=1和高速模式时、/DRDY 频率将为 fCLK/256或20MHz = 78.125kHz。

如果 同时加电序列、ADS1274 是否支持加电?

是的、如果所有电源都是同时运行的、则支持此功能。 但是、您需要在上电后使/SYNC 引脚生效、以确保器件正确复位。

此致、

基思

尊敬的 Keith:

我只给 ADC IC 加电并在18MHz 处连接 clk、我没有配置 SPI 引脚、但时钟已扩展。

DVDD->IOVDD->AVDD->VREFP ->外部振荡器(尝试新)在此顺序下,我将在发热时加电,总时钟正在扩散。

我将给出正确的电压 RANG AVDD、IOVDD 和 DVDD。 我在示波器中检查了它 。 但 IC 过热。 哪一个问题是发生的。

谢谢。此致、

阿拉文德

您好!

为了降低在加电期间损坏 ADS1274的可能性、我建议对每个电源使用线性稳压器。

此外、使用单个接地平面并将 AGND 和 DGND 引脚直接连接到 ADC 下方的散热焊盘以及内部接地平面。 下面是 ADS1274的一个示例布局。

如果 ADS1274在上电后变得很热、则它处于闩锁状态。 它可能已损坏、需要更换。 当超过器件的绝对最大值额定值时、可能会导致闩锁情况。 在上电期间、这通常是电源瞬间超过正常工作电压范围导致的。

此致、

基思