Other Parts Discussed in Thread: DAC37J82

您好、初始化 DAC37J82器件时遇到了一些问题。

我要尝试做的是在 SERDES lane0和 lane1 (RX0和 RX1)输入上设置两个 JESD 通道、将其分配到单个链路0中的 JESD 通道0和1、然后通过 A 和 B 数据路径进行传递、 并将其发送到 IOUTA 和 IOUTD 引脚。 DACCLK 引脚的输入在250 MHz 上运行、而 JESD 旨在以2.5Gbps 的速率运行、LMF=222。

在进行配置且 DAC 未输出任何数据后、我似乎遇到了奇差问题。 奇怪的是、当我尝试/K28.5/测试时、它似乎可以通过器件测试。

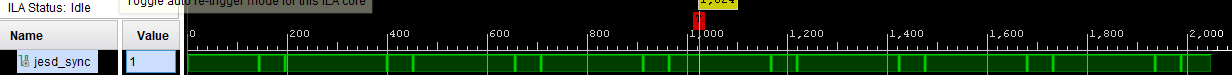

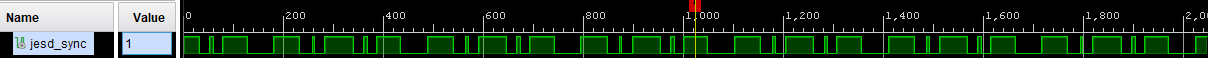

标准操作:SYNC 在重复模式中偶尔会变为低电平、但大部分时间保持高电平。 0x64和0x64状态寄存器回读0x100 (8b/10b 视差错误)

/K.28.5/测试模式:稳定 SYNC (始终为高电平)、0x64和0x64回读0x0000 (无错误)。

/D.15.1/测试模式:无同步、0x64和0x65状态寄存器回读0x400 (代码同步错误)

重复 ILA 测试模式: SYNC 在重复模式中偶尔会变为低电平、但在大多数时间都保持高电平、与标准操作类似。 0x64和0x64回读0x0000 (无错误)。

以下是我要发送到 DAC 的初始化序列(如果有用):

1.通过引脚重置 DAC 引脚

2.使用以下值对 DAC 寄存器进行编程:

Reg | Value { 0x23, 0x01ff }{ 0x1A, 0x0026 }{ 0x31, 0x1800 }{ 0x32, 0x0000 }{ 0x33, 0x0000 }{ 0x3D, 0x0088 }{ 0x3E, 0x0148 }{ 0x3B, 0x0000 }{ 0x3F, 0x0000 }{ 0x46, 0x0044 }{ 0x47, 0x190a }{ 0x48, 0x31c3 }{ 0x49, 0xFFF0 }{ 0x4A, 0x0320 }{ 0x5F, 0x0123 }{ 0x60, 0x4567 }{ 0x24, 0x0000 }{ 0x25, 0x2000 }{ 0x00, 0x211A }{ 0x03, 0xf300 }{ 0x4A, 0x033e }{ 0x4B, 0x1f01 }{ 0x4C, 0x1f01 }{ 0x4D, 0x0100 }{ 0x4E, 0x0f0f }{ 0x4F, 0x1C61 }{ 0x50, 0x0000 }{ 0x51, 0x00DC }{ 0x52, 0x00FF }{ 0x53, 0x0000 }{ 0x54, 0x00FC }{ 0x55, 0x00FF }{ 0x5C, 0x0008 }{ 0x5C, 0x0000 }{ 0x61, 0x0211 }{ 0x22, 0x101C }{ 0x02, 0x2002 }{ 0x04, 0xFCFC }{ 0x05, 0xEFF7 }{ 0x06, 0xFFFC }{ 0x14, 0x0000 }{ 0x15, 0x0000 }{ 0x16, 0x8000 }{ 0x0C, 0x01B0 }{ 0x0D, 0x0000 }{ 0x0E, 0x0000 }{ 0x0f, 0x0000 }{ 0x1E, 0x9999 }{ 0x1F, 0x8882 }{ 0x1F, 0x8880 }{ 0x20, 0x8008 }{ 0x26, 0x0000 }{ 0x2D, 0x0001 }{ 0x3C, 0x0050 }{ 0x64, 0x0000 }{ 0x65, 0x0000 }{ 0x66, 0x0000 }{ 0x67, 0x0000 }{ 0x68, 0x0000 }{ 0x69, 0x0000 }{ 0x6A, 0x0000 }{ 0x6B, 0x0000 }{ 0x6C, 0x0000 }{ 0x4A, 0x0321 }

3.通过引脚启用 DAC TX

4.从 主器件启用 JESD TX