主题中讨论的其他器件:TRF3705、

您好、TI 专家!

我遇到了 DAC3482 + TRF3705的本底噪声问题。 这种组合在大多数频率下都有效、但 2313.5MHz 附近的本底噪声非常高。

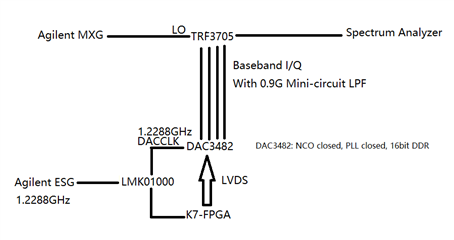

在基带板上、DAC3482在16位模式下工作、禁用 PLL 和 NCO、 DACClock = 1228.8M、X4或 X2模式。 基带波形数据在 DDR 中进行选通、其中 FPGA 读取数据、然后发送至 DAC。 测试期间、基带波形 I/Q 带宽= 100MHz。

在射频板上、有一个由 LDO 供电的调制器、没有其他组件。 DAC 输出通过900MHz LPF 连接到射频板。 DAC 和调制器都是50Ohm 系统。

测试:更改 LO 频率、按如下方式记录频谱

低电平= 2260M

低电平= 2260M

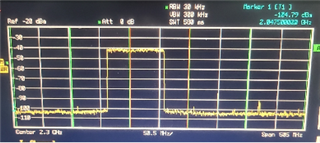

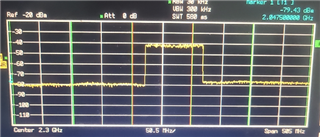

LO = 2280M

LO = 2280M

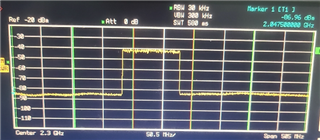

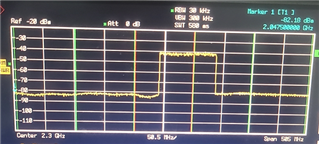

LO = 2300M

LO = 2300M

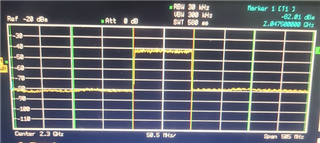

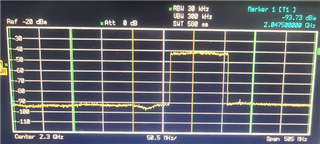

LO = 2320M

LO = 2320M

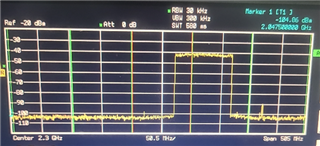

LO = 2340M

LO = 2340M

LO = 2360M

LO = 2360M

低=2380M

低=2380M

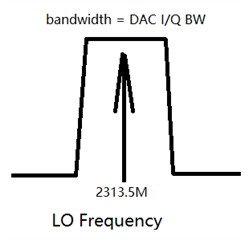

我尝试更改 DAC 时钟、基带波形 I/Q 带宽、DAC 插值 x2和 x4、发现了一条"规则"。 似乎有一个频率'窗口',中心接近2313.5M,用= I/Q BW。 如果在此"窗口"中设置 LO 频率、则本底噪声会增加。 并且 当 LO 接近2313.5M 时、噪声会变得更高。 我还尝试使用正弦波作为基带波形、本底噪声没有增加、因为正弦波频谱占用带宽= 0、似乎仍然遵守规则。

我不知道为什么会发生这种情况、如果有任何关于如何改进这一点的想法、我会非常感激。

提前感谢!

T.L.