您好!

工具链:Vivado 2022.2

IP 核心示例:基于 ZCU102 (含 GTH)

目标技术:Kintex UltraScale KU035

在移植设计期间、出现以下问题:

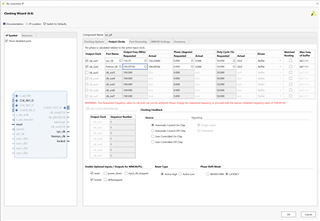

1. Xilinx 收发器 IP 向导需要从修订版6升级到修订版14

2. PLL 无法生成确切的100MHz,因此改为100.09766MHz。 DRP 时钟也设置为与 DRP 时钟的

3、创建了一个计时器来生成同步复位而不是 VIO、它由 QPLL0锁定触发并在大约4.5uS 时激活

4.将 cfg_Rx_Buffer_release_delay 设置为10 (任意值)

100MHz 时钟的 PLL 警告:

我正在测试 JESD204c IP 内核。 我创建了一个 VHDL 包装程序和一个 VHDL 测试平台来练习 IP。

测试平台:

1.将 cc_sysref_out 连接到 sysref

2. GTH ADC 至 DAC GTH

3.系统时钟= 156.25MHz

4. REFCLK = 156.25MHz

5. ADC_RX_SYNC 连接至 DASX_TX_OUT

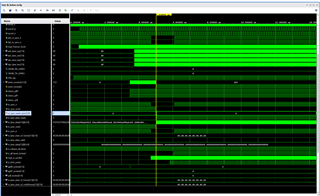

我在取消 Tx 同步复位之前看到 GTH 活动、但值是固定的(0xFF00模式)

TX 似乎在大约4.5uS 时正常启动(请参见上面屏幕截图上的光标)。

Rx 显示通道锁定在大约6uS。

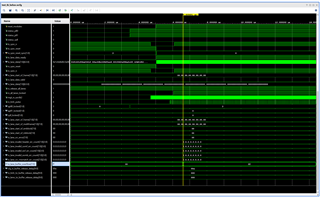

RX_LANE_DATA_VALID 从未激活、一段时间后我看到溢出错误、如下面的屏幕截图所示。

您能帮助我确定接收器未获取任何数据的原因吗?

谢谢。

伊利亚斯