Other Parts Discussed in Thread: AFE58JD28

大家好、

客户正在其项目中评估我们的 AFE58JD28、对于此器件有以下问题、您能帮助我们查看并提供一些意见吗?

-

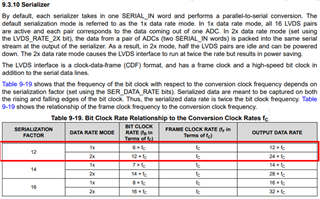

根据以下快照中的数据表规格要求、如果我们使用80MHz ADC 时钟、为了匹配最大1000Mbps、可用的 LVDS 串行化系数仅设置为12、输出 FCLK=LVDS 80MHz、480MHz、数据速率为960Mbps。

那么在这种情况下、如果我们使用数字解调器、数据 I 和 Q 都是16位的、LVDS 串行数据输出波形是怎样的? 您能帮助为我们提供有关此案例的任何示例信息吗?

-

根据产品说明书第9.3.7.2节提到的、"该器件还具有一个高速转换模式、这有助于将14位转换速率扩展至高达80MSPS。" 在这种情况下、您能帮助我们提供任何有关 SNR 规格的数据吗?

至于数字解调块、无论12位或14位数据输入、所有 I/Q 数据表输出均为16位、对于这种用例、有何注意事项吗?

谢谢。