主题中讨论的其他器件:TSW14J57EVM、、LMK04828、LMK00304

您好,

客户使用 ADC09QJ1300EVM 和 TSW14J57EVM 进行测试和验证、但遇到一些问题。 请帮助解决这些问题。 问题描述随附。

e2e.ti.com/.../ADC09QJ1300EVM-related-issues.docx

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

客户使用 ADC09QJ1300EVM 和 TSW14J57EVM 进行测试和验证、但遇到一些问题。 请帮助解决这些问题。 问题描述随附。

e2e.ti.com/.../ADC09QJ1300EVM-related-issues.docx

谢谢!

您好、Jeno:

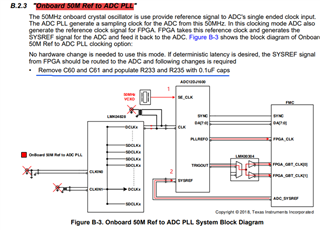

从您分享的文档来看、您好像在使用板载50 MHz 参考。 这种特定的工作模式具有一些复杂的特性。

从分享的屏幕截图中、我们可以看到 FPGA_GBT 时钟来自 ADC TRIGOUT 引脚。 此模式的工作方式是在 ADC 内部。PLL 将生成转换器时钟、s PLL 将生成串行器/解串器时钟、而 TRIGOUT 将获取串行器/解串器时钟并将其分频以输出 FPGA 时钟。 然而,只有三个分频器选项,16、32、64,这些分频器都不是与 HSDC Pro 一起使用的标准 FW 的有效默认分频器。 这就是您看到此错误的原因。

有两种方法可以解决此问题...

选项 A)

继续使用板载50 MHz 基准生成 ADC 时钟、但使用 LMK 生成基准时钟。 如果您选择此方式、则必须向 SMA 引脚 J31上的 LMK04828引脚提供时钟输入、此外、您还需要对 LMK04828和 LMK00304进行编程、以便正确生成 FPGA 参考信号并将其路由到 FMC 连接器。 这与 ADC 的外部时钟模式类似。

选项 B)

TSW14J58采集卡上有固件可支持该模式、并具有 HSDC pro 链接以获取 https://www.ti.com/tool/TSW14J58EVM

如果您对该选项感兴趣、我可以分享更详细的设置说明和 ini 文件以配置器件。

此致!

埃里克