Other Parts Discussed in Thread: LMX2592, TSW14J57EVM, LMK04828, ADC32RF45, LMH6401, LMH5401, LMX2582

主题中讨论的其他器件: TSW14J57EVM、 LMK04828、LMX2592、 LMH6401、LMH5401、 LMX2582

您好!

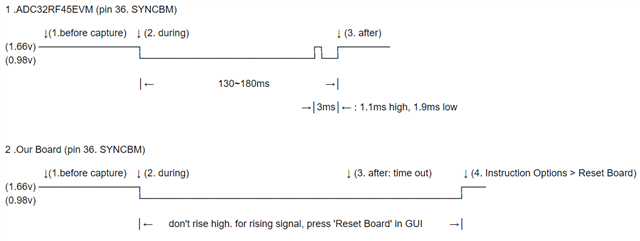

我们遇到一些问题、即我们的板无法 使用 HSDC Pro 与 TWS14J57EVM 进行通信。

当我单击捕获按钮时、我观察到一条超时消息。 SYNC 信号变为低电平、不再上升。

在 GUI 中执行"reset board"命令可将 SYNC 信号恢复为高电平状态。

不过、点击"捕获"按钮时会持续发生超时。

我们制作了 基于 ADC32RF45EVM 的定制板、用于测量高速光电探测器的信号。

我们没有 FPGA 开发环境 、并且目前按原样使用 TSW14J57EVM、因此我们决定继续 单独创建定制板。

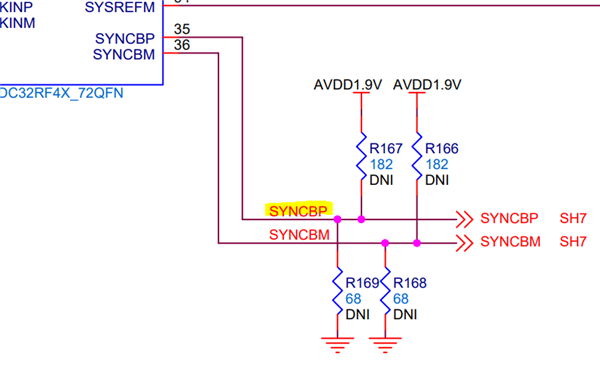

我们的 电路板包含一个微控制器(STM32F103) 、用于使用 SPI 初始化 ADC32RF45、LMK04828和 LMX2592 、以及用于信号调节的嵌入式 LMH6401、LMH5401。

在 PCB 板设计期间、芯片或连接器(FMC)之间连接的布线长度由 ADC32RF45EVM 更改。

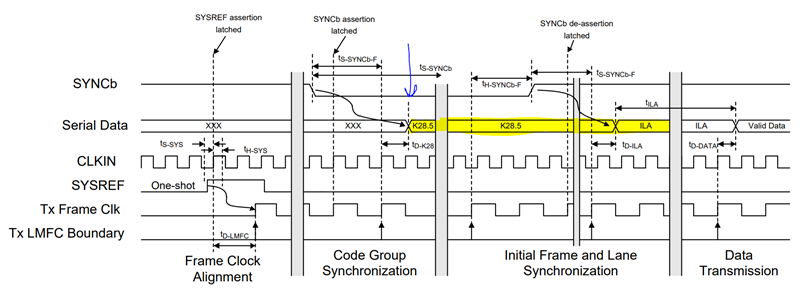

考虑到 JESD204B 标准对时序问题的敏感性、我努力平衡差分线路的长度。

由于未建立通信、我们检查了要发送到每个芯片的时钟。 我确认时钟频率与 ADC32RF45EVM 的时钟频率相匹配。

但是、由于示波器的带宽有限、无法精确测量它们之间的信号时序。

我们目前怀疑电路板之间的时钟时序和数据通道时序。

特别是、我们怀疑 与参考 EVM 板相比、数据通道的长度缩短可能会引起问题。

我们很好奇这种怀疑是否有效、以及我们是否需要调查其他方面。

非常感谢您的建议。

谢谢你。