您好、支持

目前、我们有一个通过 FMC 连接器与 DAC37j84板相连的 FPGA 电路板。 但是、FPGA 电路板的电源与 DAC 电路板侧的电源是分离的。

我的问题是:"在 DAC 侧进行下电上电时 FPGA 侧是否安全? FPGA 侧的 Tx 线是否可能对 DAC 端造成任何损坏? "

谢谢

线性

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、李先生、

FPGA 串行器/解串器发送器和 DAC37J84 RX[0:7]串行器/解串器接收器通常为交流耦合。 因此、FPGA 首次上电时的共模电压、然后 DAC37J84通过交流耦合电容器进行隔离。

请确保 FPGA 串行器/解串器发送器在 DAC 端下电上电期间*没有*任何交流摆幅。 例如、当 FPGA 首先上电时、请将串行器/解串器发送器置于 tr 状态模式、其中串行器/解串器发送器没有任何摆幅交流位。 然后、您可以为 DAC37J84上电。 DAC37J84完全上电后、可以从 FPGA 状态启用 tri 串行器/解串器发送器。

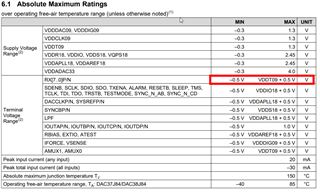

基本上、当 VDDT 为0V 时、我们要确保交流摆幅不超过绝对最大规格

-姜

Li、

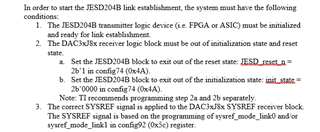

JESD204B 要求发送器侧在 JESD204状态机中保持稳定、然后重新初始化接收器状态机(即 DAC37J84)。 我建议您查看以下文档、

e2e.ti.com/.../7.3.1.2.3-Link-Initialization.docx

重点关注以下步骤:

第1步假定您已复位 FPGA JESD204状态机、请按照第2步至第3步复位 DAC JESD204接收器状态机以触发重新握手、以查看您的系统稳定性是否有所提高。

在这种情况下、您无需继续对 DAC 进行复位/重新供电