大家好!

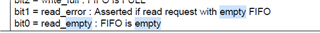

我正在尝试在定制电路板中配置 DAC38J84。 我已锁定 DAC PLL 并锁定 PLL 串行器/解串器、但无论做什么尝试、都会出现 FIFO 为空的错误。

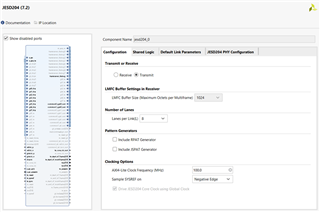

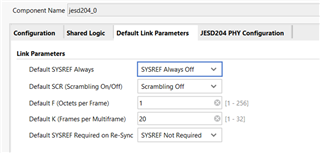

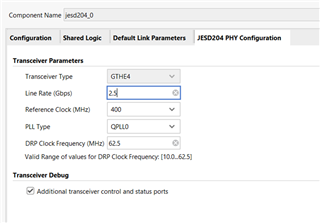

这是我的 JESD IP 内核配置:

总结:

- LMF=841模式。

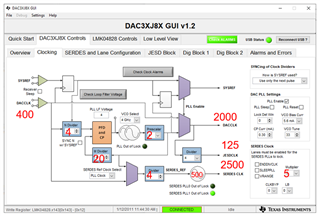

- DACCLK 基准为400MHz。

- 我将以62.5MHz 的速率(TX_CORE_CLK_OUT)发送256位。

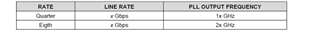

- 我的线速为256* 62.5MHz * 10/8/8= 2.5Gbps

- 内插= 8、因为我有250MHz DAC 输入速率和2000MHz DAC 输出速率。

- JESD 时钟为125MHz (2000 DAC PLL 输出/ 16 = 125MHz)、遵循 JESD_div_clk 关系=插值* L/M = 8*8/4 = 16。

- 我假设以四分之一的速率运行、因为线路速率为2.5Gbps、串行器/解串器 PLL 为2.5GHz。

- 我不使用 SYSREF。

JESD IP 内核和 DAC 中的 K、F 等参数相同。

我如下图所示配置 DAC PLL (我不使用该工具来配置 DAC、因为我使用的是自定义板、但我使用图像来解释我的配置)。

配置 DAC 后、我可以看到来自 JESD IP 内核的高电平 TX_READY 信号。 另外、TX_START_OF_MULTIFRAME 信号正在切换、因此我假设 JESD IP 内核正在从 FPGA 发送数据(我们使用的是 Zynq Ulstrascale+)。

我的问题是:

- ¿我是否正确配置了时钟? 特别是 JESD clk、我不确定它与其他时钟之间的关系。

- 在本例中、假设中的 DAC 时钟为250MHz 是正确的? 我假设这是因为我将以62.5MHz 的速率发送256位的数据包、相当于以250MHz 的速率发送64位(每个转换器16位的1个样本)。 如果正确、我假设内插值为8、因为 PLL DAC 的输出为2000MHz。

- 我设法使用 NCO 以四分之一的 DAC PLL 输出频率(2000MHz)在500MHz 处生成一个简单的音调、因此我假设 DAC PLL 按照我想要的那样进行配置。

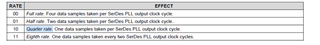

- 它是否符合以四分之一速率运行的假设? 我将我的配置基于该表:

但我还想了解该表、该表中如何定义"一个数据样本"?

话虽如此、为什么我在所有8行中都存在 FIFO 空错误?

提前感谢您的参与。