主题中讨论的其他器件:DAC81404

您好!

我们尝试在将 RFSOC FPGA 用作控制器和数据源的定制电路板上配置 DAC81404。 我们能够配置并确认所有寄存器、但我们无法按预期控制 DAC 输出通道。

我们用于初始化 DAC 的顺序如下。 值字段是我们要写入的 DAC 内部寄存器地址和数据。 例如、写入寄存器0x03时写入了0xA84

当我们写入广播寄存器或单个 DAC 寄存器通道时,我们只能看到任何一个轨电压 AVDD-AVSS。 当我们循环执行写入 DAC 寄存器的代码时、我们看到输出仅在一个特定代码处在正 AVDD 和 AVSS 之间切换、其中我们会得到中间值、 即非轨电压。 对于该特定代码以下的所有其他值、我们可以看到 AVSS 电压。

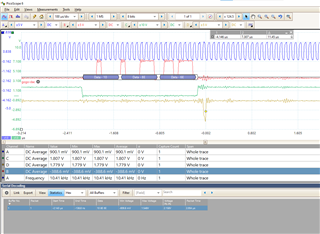

下面是示波器上的示例 SPI 抓取、同时我们将代码 x8E6E 写入 DAC 寄存器通道0寄存器地址 x10。 我们在1.8V (12MHz) IOVDD 的 SPI 最大时钟速度以下运行。

从上到下依次排列的从 A 到 D 通道为- CLK、DATA、SYNC、LDAC

我们认为、 我们可以读回的所有其他事务的 SPI 通信是正常的、并且我们没有看到任何通信问题。

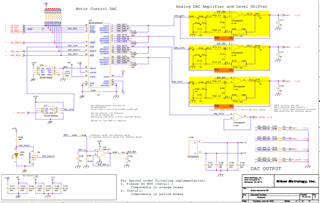

DAC 的原理图页面。

我们不确定 DAC 或板上其他东西的初始化是否存在错误。 如果您能就此问题提供帮助、我将不胜感激。