Other Parts Discussed in Thread: AFE539A4EVM

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:AFE539A4 您好!

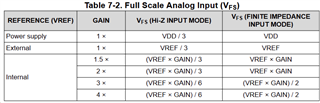

我正在使用 AFE539A4EVM 进行实验、希望获得有关正确配置以实现不同 ADC V_FS (满量程模拟输入)的确认、如表所示。

当为 Hi-Z 输入模式和4倍增益设置 V_FS =(VREF *增益)/6 如表中所示。 但是、对于有限阻抗输入模式和4倍增益、 V_FS =(VREF *增益) 它与该结果的1/2的表不同。

请确认设置寄存器的正确方法

- 提供 Hi-Z 输入模式和4x 增益

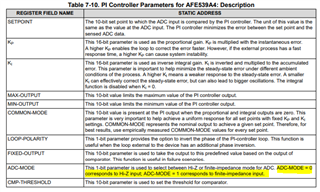

- DAC-A-VOUT-CMP-CONFIG = 0x1405

- DAC-D-VOUT-CMP-CONFIG = 0x1405 (看起来该功能未使用) D 通道 需要设置为等于 A 通道 )

- ADC 模式0x27[1]= 1

- 支持 有限阻抗输入模式和4x 增益

- DAC-A-VOUT-CMP-CONFIG = 0x1401

- DAC-D-VOUT-CMP-CONFIG = 0x1401 (它似乎未使用 D 通道 需要设置为等于 A 通道 )

- ADC 模式0x27[1]= 0

此致!

菲尔