Other Parts Discussed in Thread: ADC12DJ3200EVM, ADC12DJ3200, LMK04828

主题中讨论的其他器件: LMK04828、 ADC12DJ3200

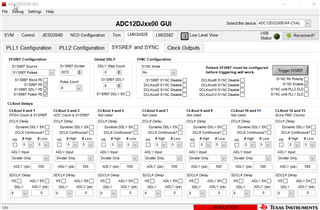

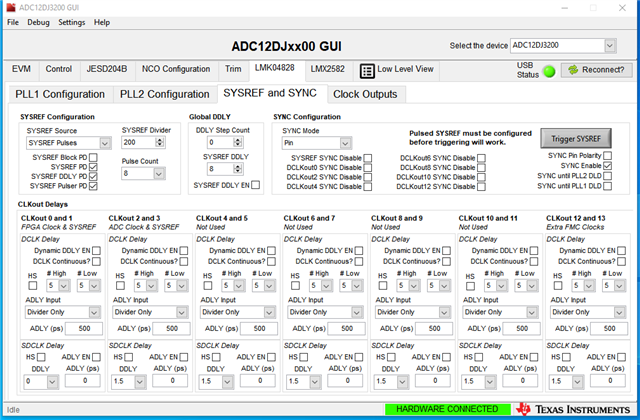

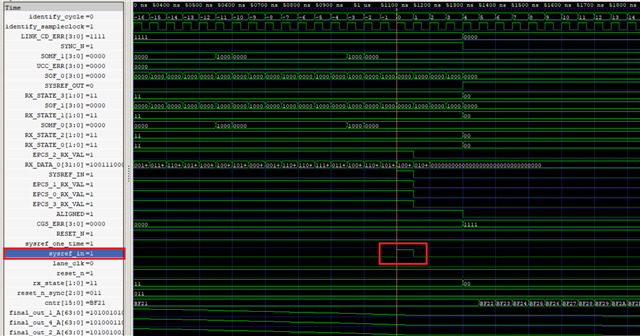

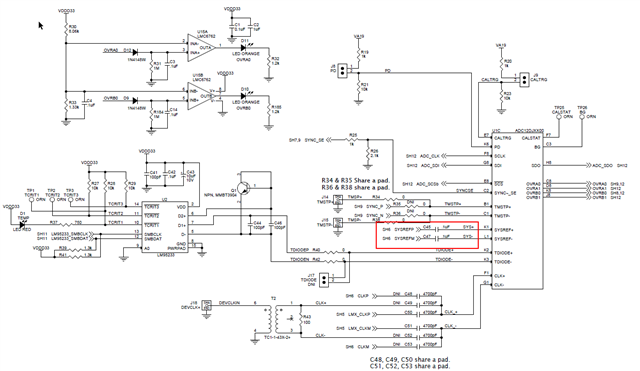

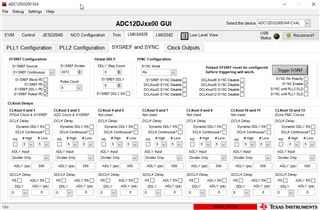

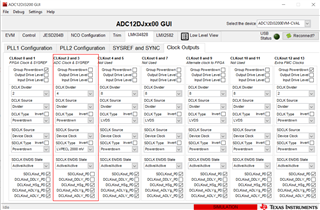

我使用的是 ADC12DJ3200EVM 电路板。 我想了解在子类1中生成一次性 SYSREF 的过程。 配置值如下所示

L = 4

M = 4

F = 8

数据速率= 5Gbps

另外、我想了解在打开电源之后、在单次触发模式下或在连续或周期模式下 ADC 转换器对 SYSREF 进行采样的时间。 我需要在下电上电后添加 SYSREF 生成的延迟吗? 我参考下面的链接,但仍然不清楚如何配置不同的参数梗死部分参数不可编辑。

https://www.ti.com/lit/ta / ssztcl6/ssztcl6.pdf

请帮我解答上述问题吗?