Other Parts Discussed in Thread: DAC7718

您好!

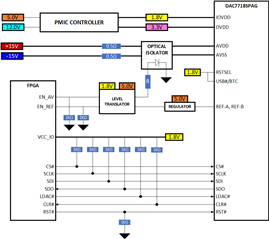

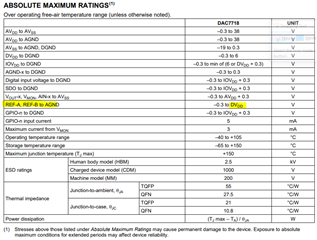

我将在我设计的电路板上使用 DAC7718SPAG。 我可以看到在我释放重置线后、VOUT X 线路变为大约9V。 这似乎

很奇怪、因为我预计它们会保持在0V。

我有以下与此相关的附加信息:

RSTSEL = USB#/BTC = IOVDD = 1.8V

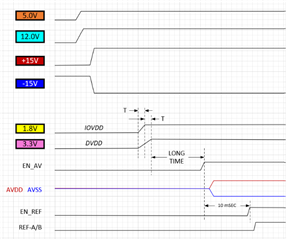

IOVDD = 1.8V (首先加电)

DVDD = 3.3V (第二个上电)

AVDD =+15V(第三和同时供电)... AVSS =-15V

REF-A = REF-B = 4.096V (最后通电)

根据数据表、这应该会按如下方式配置 DAC:

双电源

二进制补码(输入格式)

VOUT = 0V (RST#变为高电平后)

但是、我要说明的是、AVDD/AVSS/REF-A/B 全部由 FPGA 启用。 此时、我要对 FPGA 进行编程、

的快照。 完成编程并手动移除跳线后、该逻辑会自动启用 AVDD 和 AVSS、

等待大约10ms 并启用 REF-A / REF-B。 因此、从 IOVDD 和 DVDD 到这三个电源存在"人机速度"延时

信息。

这会发出红色标志吗? 数据表中详细说明了电源定序、但并未说明器件数据表

输出范围。

感谢您的任何见解和想法。 谢谢!