主题中讨论的其他器件:DAC38RF82、

DAC38RF82上电时 SYNC 信号为高电平

调试 DAC38RF82时遇到问题、芯片上电后、在没有 JESD204B 链路设置的情况下、它仍然保持高电平。

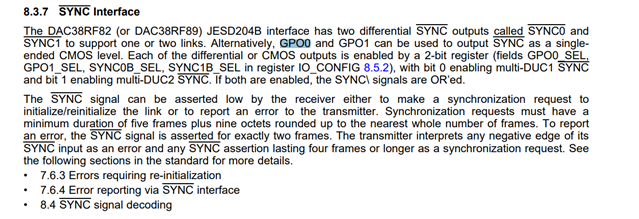

在204B 协议中、接收器 DAC 应使用 SYNC 信号来发送同步请求、DAC 应首先将 SYNC 设置为低电平以在它通电时发送同步请求。 然后在接收到发送方发送的 K 代码(BCBC)并完成链路同步后将 SYNC 拉高。 但现在 SYNC 在上电后一直处于高电平、甚至在配置寄存器后也没有被拉低、这是寄存器配置错误还是芯片硬件有问题? 在什么情况下 SYNC 将始终保持高电平? 芯片电路板为 DAC38RF82EVM。

时钟电路使用 DAC38RF8xEVM 中的板载 VCXO 时钟模式(CMODE4)模式、使用120MHz 替换电路板的 VCXO、更改寄存器设置、VCO 频率为2.5GHz、DAC 时钟输出的 DACCLK+频率为2.5GHz、SYSREF+为9.765625MHz、 且 DAC 的 PLL 被禁用。

jesd204B 配置 TX-HD 1 L-M-F-S 41121中断=1

输入速率2500 (MSPS) fDAC 最大2500MSPS

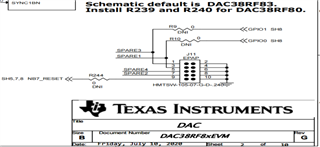

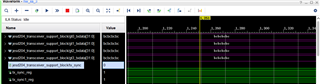

如下图所示、DAC38RF82EVM R9和 R10短接、并在寄存器中启用 GPO0和 GPO1

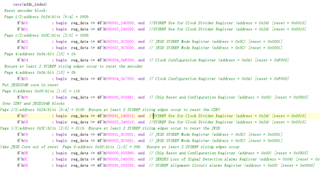

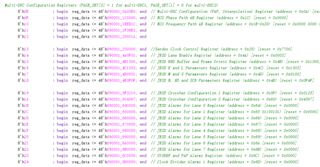

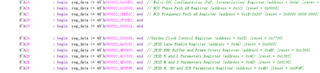

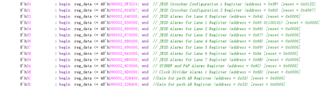

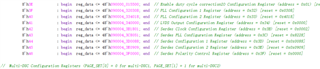

DAC 寄存器设置如下:

下图显示了每个链路的链路建立顺序,

链路建立过程如下:

1.初始化 FPGA (XCKU060-2FFVA1156I) jesd204B IP 内核;

2.复位 DAC 使用 DAC38RF82EVM 上的 SW1;

初始化 DAC 寄存器。