请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADS9227EVM 我决定打开另一个问题、因为这更多地是有关 EVM 的操作。

我将尝试描述 ADC 在不同采样率下的运行情况、因此我将尝试为 EVM 提供外部时钟。

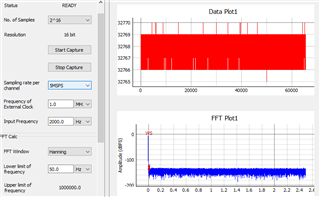

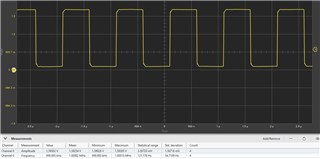

我正在向 J6提供1MHz 1.8V 峰值方波、测量结果如下:

JP5经过修改以支持 EXT_CLK。

但我必须做错了事、因为结果是完全错误的:CH2的输入端连接到 GND。

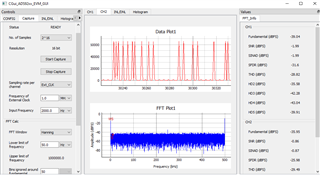

相比之下、这是默认 FPGA 时钟下的结果: