主题中讨论的其他器件: LMK04821

您好!

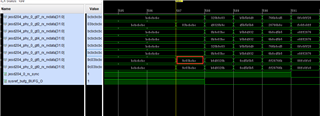

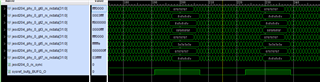

我正在使用 adc12qj1600 ,我的采样率是1Gsps,并使用 jmode0,km1=31。但我发现当同步较低时我无法接收 k28.5。我捕获的通道数据如下所示。

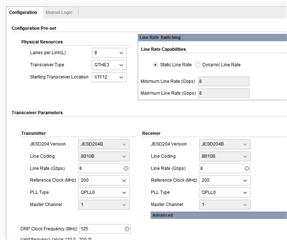

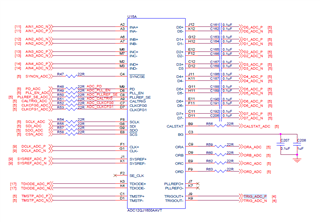

ADC 的寄存器配置如下所示

{ 0x0000、0xB0 }、//#RESET 寄存器模拟组主页。750ns 自清零

{ 0x0270,0 },//在继续读取 INIT_DONE 之前验证器件初始化已完成,直到返回1。

{0x02c1、0x3F}、//ALM_STATUS

{0x02c4、0xFF}、//FIFO_LANE_ALM

{ 0x002B、0x15 },

{0x002A、0x02}、//sysref_LVPECL_en = 1 dclk_LVPECL_en = 0

{0x0057、0x00}、//TRIGOUT_EN = 0

{0x0057、0x01}、//TRIGOUT_EN =0 32DIV

{0x0057、0x81}、//TRIGOUT_EN =1 32DIV

{0x0200、0x00}、//JESD_EN = 0

{0x0061、0x00}、//CAL_EN = 0

{0x0201、0x00}、//JMODE = 0

{0x0202、0x1F}、//K = 32 = KM1 + 1

{0x0204、0x00}、//SYNC_SEL;OFFSET BINARY;8B/10B 扰频器已禁用

//

{0x0048、0x00}、//预加重,(如果需要)

//报警

{ 0x02c2,0x02 },//取消屏蔽所有警报

{0x0205、0x00}、//测试模式(如果需要)

{0x0062、0x01}、//CAL_CFG0、禁用 BG;禁用 OS;禁用 BG;启用 FG

{ 0x0061、0x01}、//CAL_EN = 1、启用校准状态机

{ 0x0029、0xA0 },

{0x0029、0xF6}、//SYSREF_PROC_EN=1、SYSREF_RECV_EN=1、SYSREF_ZOG=1、设置 SYSREF_SEL

{0x0200、0x01}、//JESD_EN = 1、重新启动 JESD 链路

{ 0x006c、0x00}、//cal_soft_trig 触发 FG

{ 0x006c、0x01}、//cal_soft_trig 触发 FG

{ 0x02c1,0x3F }

您能帮我解决这个问题吗?