我很难从数据表中找到可以以菊花链形式连接多少个器件。

我想使用 一位流到 FPGA。

我想以菊花链形式将8个器件连接64个通道。

tc (DCLK)周期 DOUT 到 DIN 菊花链连接"的规格为29.8ns。

这是否意味着我需要一个8 x 29.8 = 238.4ns (4.19 MHz)的 tc (DCLK)周期?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Ton:

通道的最大数量取决于多种设置和配置。 tc (DLCK)最小值为29.8ns、这会将最大数据时钟(DCLK)频率限制为33.557MHz。 这也是 ADC 时钟的最大时钟频率。 考虑到 DOUT0上的传播延迟、这是满足 DIN0设置和保持时间要求所必需的。

下面我尝试将所有这些设置合并到一个公式中、以计算 菊花链中 L18器件的最大数量 N、其中通道总数将为8*N。

N=(CLK_DIV*OSR*TDM)/(DCLK_DIV*TDM*4 Packet_Size),其中计算出的 N 值向下舍入到最接近的整数。

CLK_DIV 是 ADC 数据速率的时钟分频设置、其中 CLK_DIV 可等于1、2、3、4或8。

OSR 是数字滤波器的过采样率设置;有关可用的 OSR 设置和产生的数据速率、请参阅表6-1至6-5。

TDM 是使用的 DOUT 引脚数;1、2或4在菊花链模式下可用。

DCLK_DIV 是输出数据速率的数据时钟分频设置、其中 DCLK_DIV 可以等于1、2、4或8。

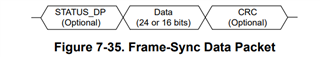

Packet_Size 是每帧每通道的位数、即16、24、32或40、具体取决于16b 或24b 数据、可选的状态字节和可选的 CRC 字节。

在您的特定用例中、您希望仅使用 DOUT0引脚(TDM = 1)以菊花链方式连接8个 ADS127L18器件(N = 8)、总共64个通道。 假设您未启用 CRC 或状态字节、那么每个通道的数据包大小将为24、以支持24位读数。 我还将假设 DLCK_DIV=2和 CLK_DIV=3以支持尽可能高的数据速率。

根据这些假设、支持的最小 OSR 值(最大数据速率)将为:

8=(3*OSR*1)/(2*24*4)

OSRmin = 512

在高速模式下且65.536MHz、21.845MHz 和32.768MHz 时、这将导致每通道的最大可能数据速率为21.3ksps。

此致、

N·基思

精密 ADC 应用

尊敬的 Ton:

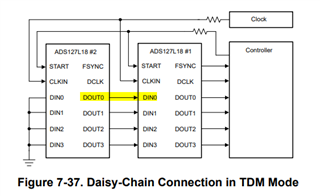

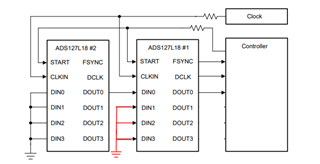

您只需要一行 DOUT0。 我重新绘制了原理图、展示了总共8个 ADS127L18中的2个、希望可以使这一点更加清楚。

由于您的最大采样率为8192Hz、该值小于此21300Hz 配置中支持的最大采样率、因此这很有效。 我建议使用 OSR 设置1024、这将进一步提高 SNR (有效分辨率)。 在这种配置下、所有 ADS127L18的主时钟频率 CLKIN 需要调整为8192*1024*2*3=50331648Hz。

将50MHz 的标准值时钟频率与这些设置一起使用将使每个通道的数据速率为8138Hz、略低于您的目标、但您可以自定义顺序振荡器或使用可编程 PLL 来生成实现所需数据速率所需的确切50.331648MHz 频率。

此致、

基思