主题中讨论的其他器件: XTR111

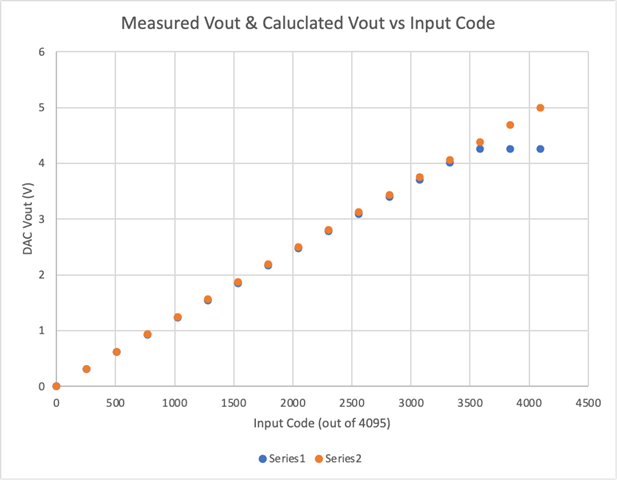

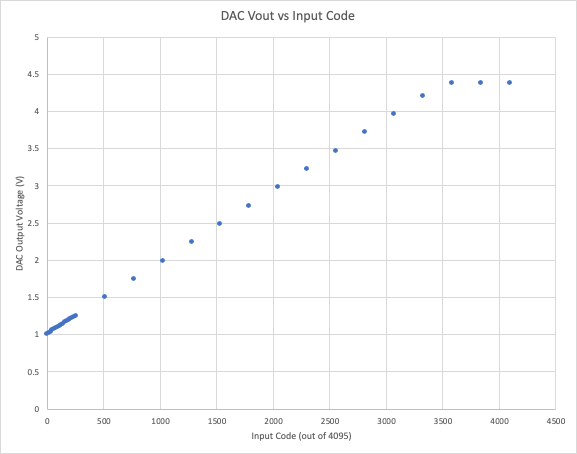

您好、在输出电压被削波至大约4.25V 至4.37V 的特定点之前、DAC7551输出电压的运行十分干净有一个问题。

我已经检查了 Vdd 和 VrefH (均连接到5V)、并验证了它们是稳定的5V 额定电压、并且通过 SPI 的输入通信的行为也符合预期。

我的主要困惑是为什么会发生这种削波。 数据表指出额定值 VrefH 允许它进入正轨、所有其他电源和 GND 连接看起来稳定。

当我用 FFFFh 加载 DAC 时-与"正轨上的拉电流"特征图一样-输出最高可达5V。 我的初始想法告诉我、这意味着我的 DAC 电路能够推进到满量程、但也许技术人员可以更深入地了解发生这种情况的原因。 从另一个角度来看、我还认为可能存在阻抗不匹配的情况、并且 FFFFh 代码(根据数据表、操作码将此指定为" Hi-Z "操作)为其提供了适当的阻抗。

综上所述、我倾向于这样一个事实、即 VrefH 可能不够高、并且可能需要一些上动态余量才能在满量程运行、正如削波电压时的预期情况。 但是、由于数据表中声称输出应该能够达到正轨-高达 VrefH、我对此持怀疑态度。

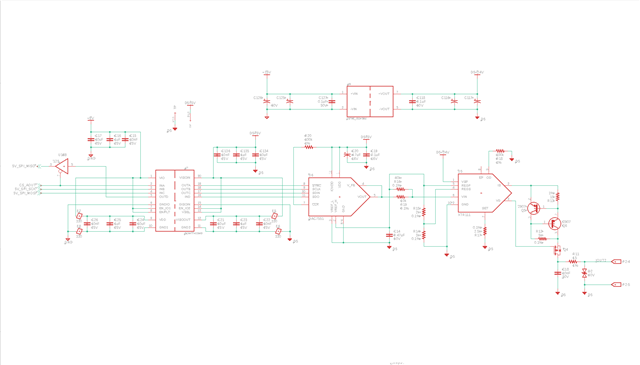

我已经根据 DAC Vout 电压测试输入值、并随附了数据图。 我还要附加原理图和代码片段、以便我用于测试输入代码。

注意:虽然原理图是完整电路、出于测试目的、我也探测了未连接 XTR 电路的 DAC Vout、以消除影响电路运行的可能性。 此外、对于测试代码、我使用 NUCLEO-L476RG 开发板、通过 SPI 与芯片通信。

测试代码:

//输出代码:将 aout_arry[0]和 aout_arry[1]结合使用时为0x0fff

//aout_arry 已初始化为 uint8_t 类型

aout_arry[0]= 0x0F;

aout_arry[1]= 0xff;

csAout2 ();//丢弃同步信号

HAL_SPI_TRANSMIT (&hspi1、aout_arry、21000);//发送输出代码

writeCshi ();//提高 SYNC 信号以更新寄存器