主题中讨论的其他器件: AFE881H1

您好!

我正在尝试从我的微型到上述 HART 调制解调器设备发送数据。

执行的步骤为

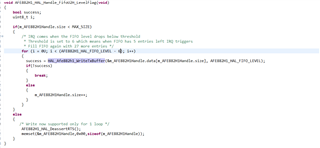

将阈值设置为3、这意味着在数据 FIFO 中的6个级别之后将生成 IRQ

将数据写入 FIFO U2H (HART 已在配置中启用) FIFO 写入高达32级

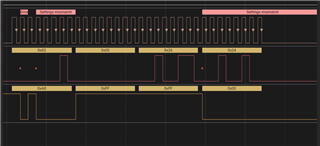

RTS 生效

等待 CTS 有效

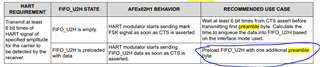

在该之后、AFE882H1将自动开始向 MOD_OUT 引脚发送数据、因为数据已经在 FIFO 中

IRQ 到达后(如果 FIFO 到达6级)、再次使数据排队、直到 HART 帧完成。

这里有1个问题

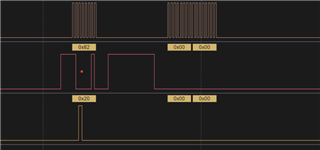

首先,建议发送前导码字节,因此32级中的1级是前导码字节,右是我要发送2个前导码字节和10个字节的数据(全0)。

是什么顺序?

0x15(fifo reg wr ) 0x01 (奇偶校验)数据(0xFF 前导码)现在我应该继续写入数据, FIFO 指针将自行增加

0x15 (fifo reg wr) 0x01 (奇偶校验)数据 (0xFF 前导码 )(数据 (0xFF 第二前导码字节) 数据(0x00实际数据)数据(0x00 实际数据)同样地

或者对于每个字节、需要发送

0x15(fifo reg wr ) 0x01 (奇偶校验)数据(0xFF 前导码)

0x15(fifo reg wr ) 0x01 (奇偶校验)数据( 0xFF 第二前导码字节)

0x15(fifo reg wr ) 0x01 (奇偶校验)数据(0x00实际数据)

0x15(fifo reg wr ) 0x01 (奇偶校验)数据(0x00实际数据),直到传输10字节

谢谢。

阿尔蒂