主题中讨论的其他器件:DAC38RF82、 LMK04828、LMK04832

您好!

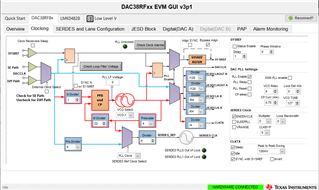

我正在使用评估板(DAC38RF82EVM)和 TSW14J57信号发生器评估 DAC38RF82。

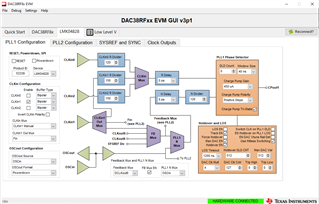

100 MHz /+6dBm 信号馈送到 LMK (J4连接器)的输入端。

通过以下配置、一切正常、可在 DAC 输出端获得正确信号。

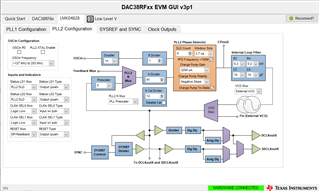

现在、目标是提高 DAC 时钟频率、以便在 DAC 输出端从2000 MHz 到3600 MHz 生成信号。

我始终将系统的100 MHz 基准并使用低 PLL 分频器值(为了获得良好的相位噪声)、我想在8800 MHz 下使用 DAC 频率(频率值处于高频带 VCO 的频率范围)。

使用以下配置、要馈送到评估板上 J4连接器的信号的频率是1100 MHz! 目的是保持100 MHz 作为频率基准...

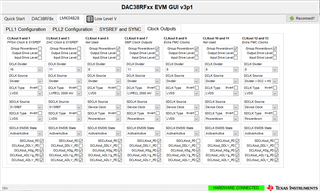

通道数已增加(从4个增加到8个)、以获得较低的串行器/解串器通道速率。

有人能解释一下在这种情况下为什么需要1100 MHz 信号吗?

难道是因为 DAC 芯片本身的缘故吗?

还是由于评估板的架构?

感谢您的帮助!

阿兰