您好!

我正在阅读 有关 TI_204C_IP 的参考设计(zc706_8b10b)。

我有关于 sysref 的问题。

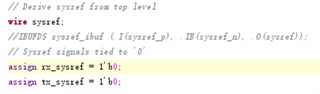

在 TI_204C_IP_Ref.SV 中、我看到 Sysref 信号绑定到"0"、如下所示。

那么、为什么在 参考设计中这么做呢?

谢谢

此致

丹尼尔

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Amet:

感谢您的回答。 我还有两点需要您的帮助。

1.关于 TI_204C_IP 的 PARAM_TX_K。

从 TI204c-IP-User's Guide 中、 (PARAM_TX_F * PARAM_RX_K * 8)的值必须是 TX_LN_DATA_WIDTH 的整数倍数。

此外、根据 JESD204B 标准、K 的值应为"ceil (17/F)≤K≤min (32、FLOOR (1024/F))"。

我的 LMFS=8212和 TX_LN_DATA_WIDTH=64、 PARAM_TX_K 似乎仅为24或32。 是这样吗?

2.我们使用 DAC38J82,但我们对 SYNCBP/SYNCBN 犯了错误布局。

这意味着我们不能将该信号传递到 TI_204C_IP 的 DAC_TX_SYNC_n。

您是否有任何建议建议不要使用 SYNCBP/SYNCBN?

谢谢

此致

丹尼尔

Daniel、您好!

1>正确。 K 的唯一选项是24或32。

2>如果 DAC 和 FPGA IP 之间未连接 SYNC 信号、可尝试以下操作:

i>配置 LMK 时钟芯片以生成时钟和 SYSREF

i>使用 FPGA 中的寄存器来控制 TX_IP 的 SYNC 输入。 强制 SYNCn 信号为"0"。 这将强制 TX_IP 保持在 CGS 模式

III>配置 DAC 以启动链路。 此时、DAC 应检测到 CGS 并将其同步输出从"0"更改为"1"。

iv>强制 SYNCn 信号为"1"。 这将使 TX_IP 从 CGS 转换到 ILAS 并进入活动数据状态。 希望 DAC 会检测这些更改并锁定至 TX_IP。

请注意、我不确定该序列是否能保证适用于 DAC38J82。 您将需要对其进行试验并检查行为。 如果在 DAC 中实施了某种形式的超时(在 CGS 和 ILA 状态之间)、则会产生错误。 遗憾的是、在这种情况下、唯一的选择是修改电路板、从而正确连接 SYNCn 信号。

此致、

艾米特