大家好,

我在数据采集系统项目中工作、因此我们需要8通道输入在此情况下、我们选择 ADS1278。 要通过 SPI 协议配置 ADS1278、

我们 通过 I/O 引脚配置

ADS1278 输入引脚 - 测试 PIN[0:1] //该引脚设置为 低电平 因为我们使用 正常模式 。

ADS1278输入引脚- 格式 PIN[0:2] //此引脚设置为低电平 ,因为我们使用了 SPI TDM 动态格式。

ADS1278输入引脚- 模式 PIN[0:1] //该引脚设置为 低电平 ,因为我们使用了高速模式。

ADS1278输入引脚- POWER DOWN PIN[0:8] //该引脚设置为 高电平 ,因为我们使用了 8通道输入。

ADS1278输入引脚- CLKDIV 引脚1 //此引脚设置为 高电平 ,因为我们需要更高的每秒采样数。

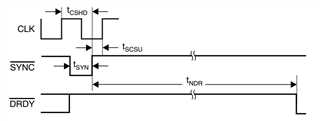

ADS1278输入引脚片选/SYNC 引脚1 //该引脚被设置为 高电平或低电平(基于条件)。

ADS1278输出引脚- DRDY 引脚1 //读取引脚。

FCLK = 25MHz

SCLK = 25MHz

在完成配置后、

第一 芯片选择/同步 引脚置于低电平

在监测 DRDY 引脚//当引脚为 L 时 功 移动下一个条件。

在 SPI 中、写入24字节、DATA=0将发送/也发送24字节的 SCLK 也会发送。

但是、借助 SPI 读取功能、

芯片选择/同步 引脚放置 高 ...... 此时 DRDY 引脚设置为 高

如何检索数据...?

请给我一个参考代码。

谢谢。此致、

Aravind. SR