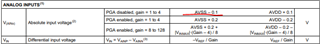

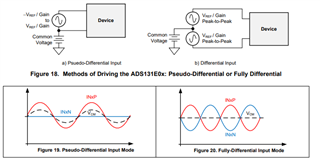

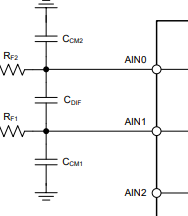

我们使用 Ain0和 Ain1来测量伪差分 ±2.0V 信号。 我们的 AVDD 和 AVSS 为±2.5V、并且使用 AVDD 和 AVSS 作为基准。 ADC 输入之前的信号电流终端是 Cdiff 为10nF、CCM 为1nF 的配置。 我们没有使用 PGA、并且已对寄存器进行设置以绕过 PGA。

问题在于、对于大于60-70mV 的信号、内部 ESD 二极管似乎会激活、从而将读数驱动至0V。

我们尝试了变频 Cdiff 和 CCM、在 AIN 前添加电感器、在 AIN 前添加电阻器、并将共模电压从-2.5V 更改为0V。

我们已经测量了上述测试的进度、在二极管激活前测量到高达700mV 的电压。 遗憾的是、我们尚未能执行满量程测量。

如需任何有关如何端接差分输入的帮助或参考文档、我们将不胜感激。