主题中讨论的其他器件:TM4C1294NCPDT、、 ADS1278

您好、TI 团队、

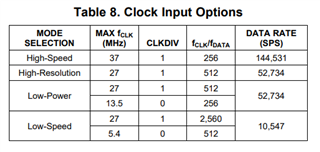

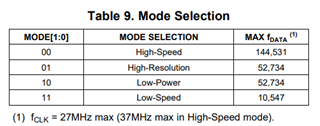

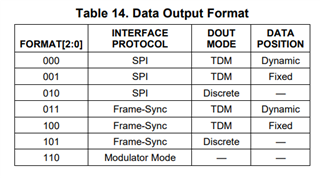

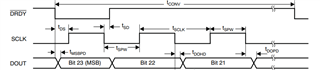

我们将使用 TM4C1294NCPDT 微控制器与 ADS1274 ADC 模块互连。 如果我们一次仅连接一个通道、则会得到正确的数字值。 但是、当我们连接了多个通道时、表示 ADC 数字值变得不正确。 例如,连接通道1和2意味着获得不正确的数字值,连接通道1、2、3和4意味着获得不正确的数字值等。

请引导我们什么可能是导致的问题。 我将下面的 ADC 原理图作为附件、

提前感谢、

此致、

A. Ajith Kumar