请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC12DJ3200EVM 您好!

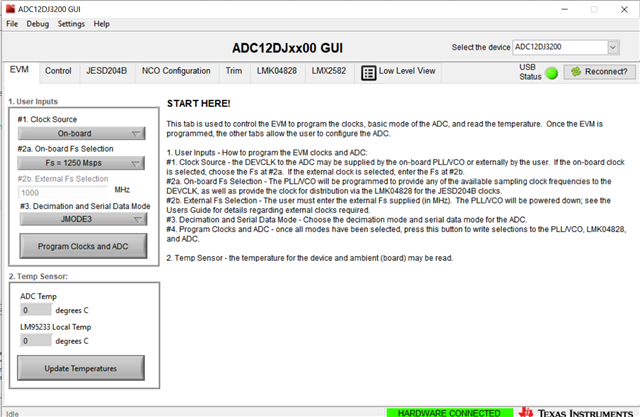

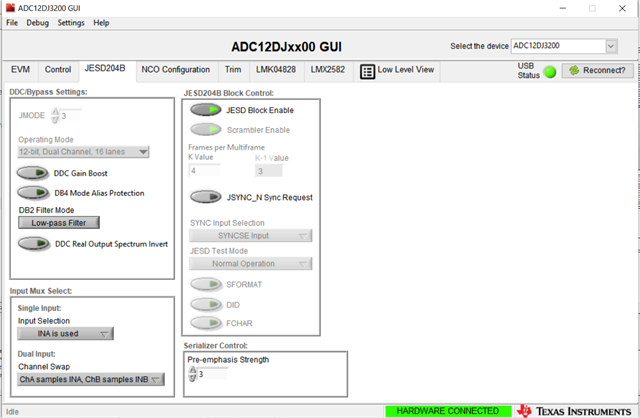

我正在使用 ADC12DJ3200EVM 和 Microchip FPGA 板来验证 Microchip 的 JESD204BIP 的功能。 我想以每条通道2.5Gbps 的数据速率运行 ADC、并配置 JMODE - 3和 FS = 1250、如以下快照所示。 理解是,对于此配置,ADC12DJ3200EVM 会为 FPGA 生成62.5MHz DEVICE_CLK。 这种理解和配置是否正确?