Other Parts Discussed in Thread: ADS127L11

工具与软件:

你好

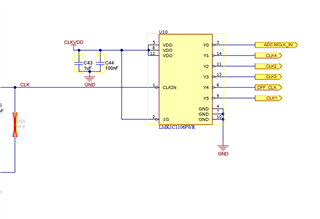

我正在设计一个 PCB、要在菊花链模式下连接2个 ADS127L11。

我正在查看 同步采样系统中的 ADS127L11 和 TIDA-010249。

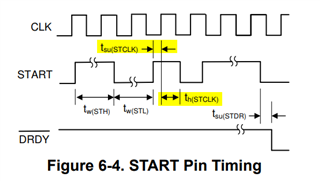

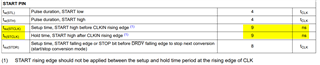

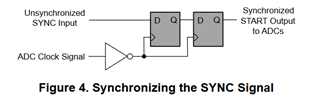

在 Simuloues 中、采样文档的 ADC 时钟在开始/同步电路中反相。 我们希望触发器在时钟的下降沿触发是有意义的、这样可以摆脱1周期不确定性。

不过、在参考设计的原理图中、不会发生此类反转。

我缺少什么吗? 或者参考设计中是否存在错误?

为什么使用2个 D 触发器? 这还不够吗?

感谢您的帮助