工具与软件:

你好

我正在设计一个 PCB、要在菊花链模式下连接2个 ADS127L11。

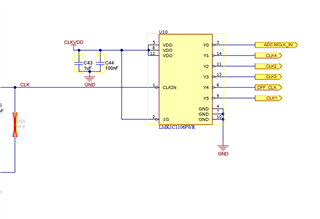

我正在查看 同步采样系统中的 ADS127L11 和 TIDA-010249。

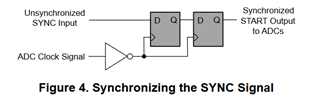

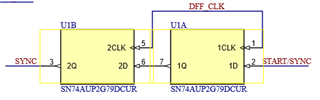

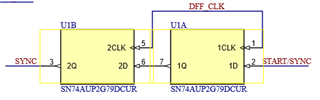

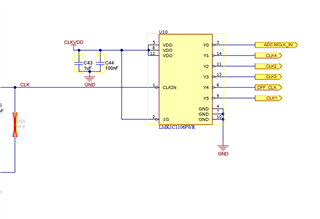

在 Simuloues 中、采样文档的 ADC 时钟在开始/同步电路中反相。 我们希望触发器在时钟的下降沿触发是有意义的、这样可以摆脱1周期不确定性。

不过、在参考设计的原理图中、不会发生此类反转。

我缺少什么吗? 或者参考设计中是否存在错误?

为什么使用2个 D 触发器? 这还不够吗?

感谢您的帮助

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

你好

我正在设计一个 PCB、要在菊花链模式下连接2个 ADS127L11。

我正在查看 同步采样系统中的 ADS127L11 和 TIDA-010249。

在 Simuloues 中、采样文档的 ADC 时钟在开始/同步电路中反相。 我们希望触发器在时钟的下降沿触发是有意义的、这样可以摆脱1周期不确定性。

不过、在参考设计的原理图中、不会发生此类反转。

我缺少什么吗? 或者参考设计中是否存在错误?

为什么使用2个 D 触发器? 这还不够吗?

感谢您的帮助

您好 Jonas:

很好的发现、这是一个错误。 但是、在最坏的情况下、4x ADS127L11将不同步1个 CLK 周期。 我认为我们在参考设计中没有注意到这一点、因为 SYNC 信号已经与 CLK 信号同步(PHI 控制器卡上的 FPGA 使用16MHz CLK 振荡器进行计时)。

双触发器增加了输出完全稳定的可能性、因为单级触发器可能具有一小段时间的元稳定性、具体取决于输入转换的时序和时钟。 建议的电路是两个时钟域之间的数字同步的经验法则、根据您所使用逻辑的确切特性、单级触发器可能就足够了。

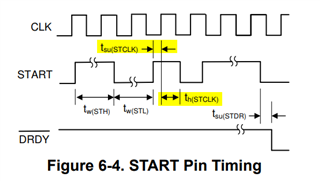

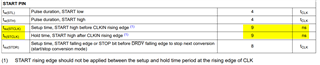

另请注意、只要能够满足数据表图6-4所示的时序、就不需要触发器、这通常是主机处理器/FPGA 使用用于 ADC 的相同时钟源时的情况。

此致、

N·基思

精密 ADC 应用