主题中讨论的其他器件:ADS8685

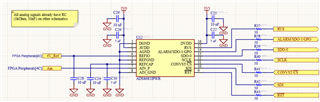

工具与软件:

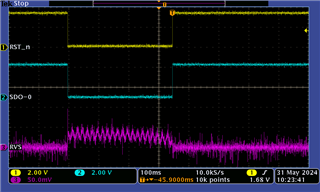

这是我第一次使用该器件。 所有接地均连接到同一个返回平面。 初始上电或复位时(RST_n 引脚被驱动至3.3V)、RVS 引脚保持低电平。 根据数据表的第7.4.2.1节:"为了退出任何复位状态、RST 引脚必须在 CONVST/CS 和 SCLK 保持低电平的情况下被拉高。 延迟 TD_RST_POR 或 TD_RST_APP 后、器件进入 ACQ 状态且 RVS 引脚变为高电平。 我读取这意味着 CONVST/CS 应与 SCLK 一起保持低电平、直到 RVS 变为高电平。 请告知。

请告知。 我使用一个使用3.3V I/O 的 FPGA 来驱动器件。

DGND = 0V

AVDD = 5.2V

AGND = 0V

REFIO =~4.09V

REFGND = 0V

REFCAP =~4.09V

AIN_P =未连接

AIN_GND = 0V

RST_n = 0V 或3.3V

SDI = 0V

CONVST/CS_n = 0V (FPGA 正在等待 RVS 变为高电平、然后再开始转换)

SCLK = 0V

当 RST_n = 0V 时、SDO-0 = 0V;当 RST_N = 3.3V 时、SDO-0 = 3.3V

警报/SDO-1/GPO = 0V

RVS = 0V

DVDD = 3.3V