工具与软件:

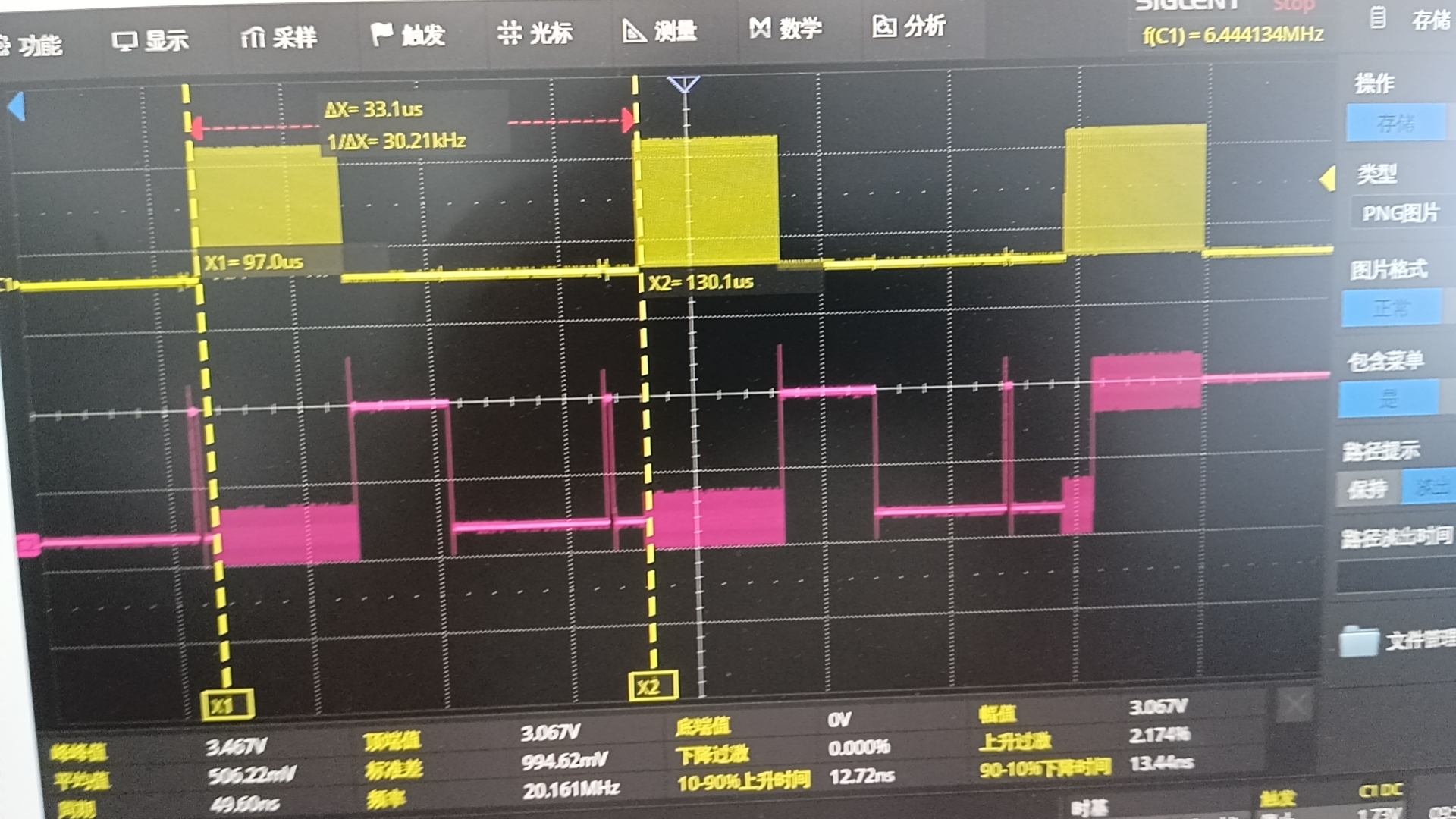

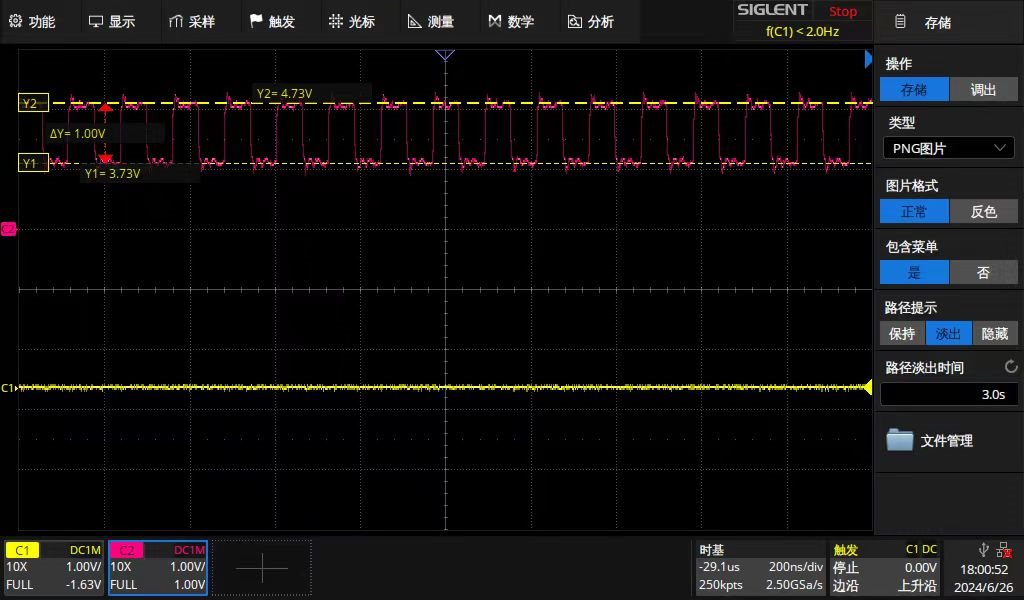

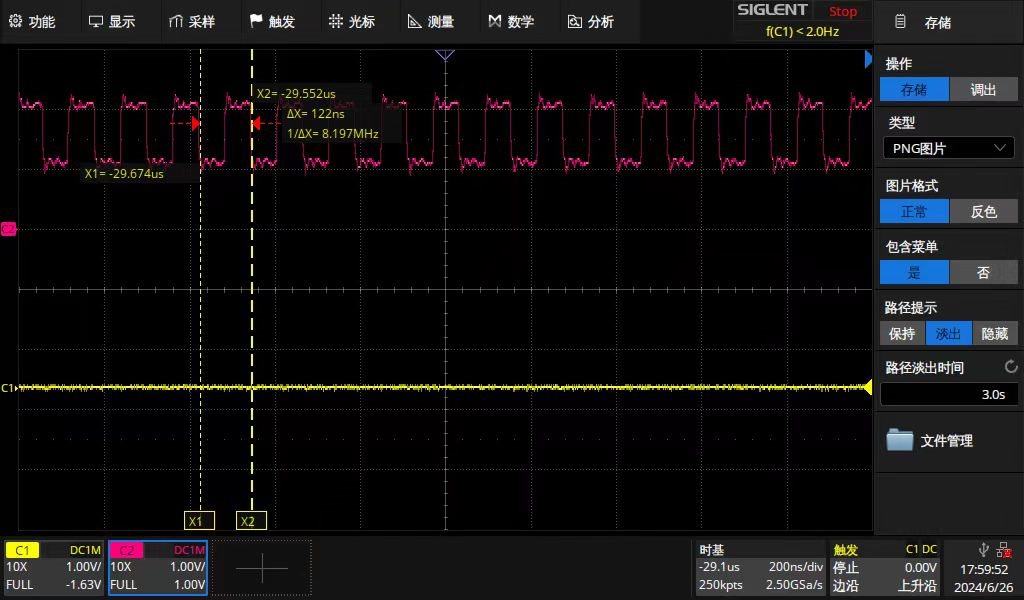

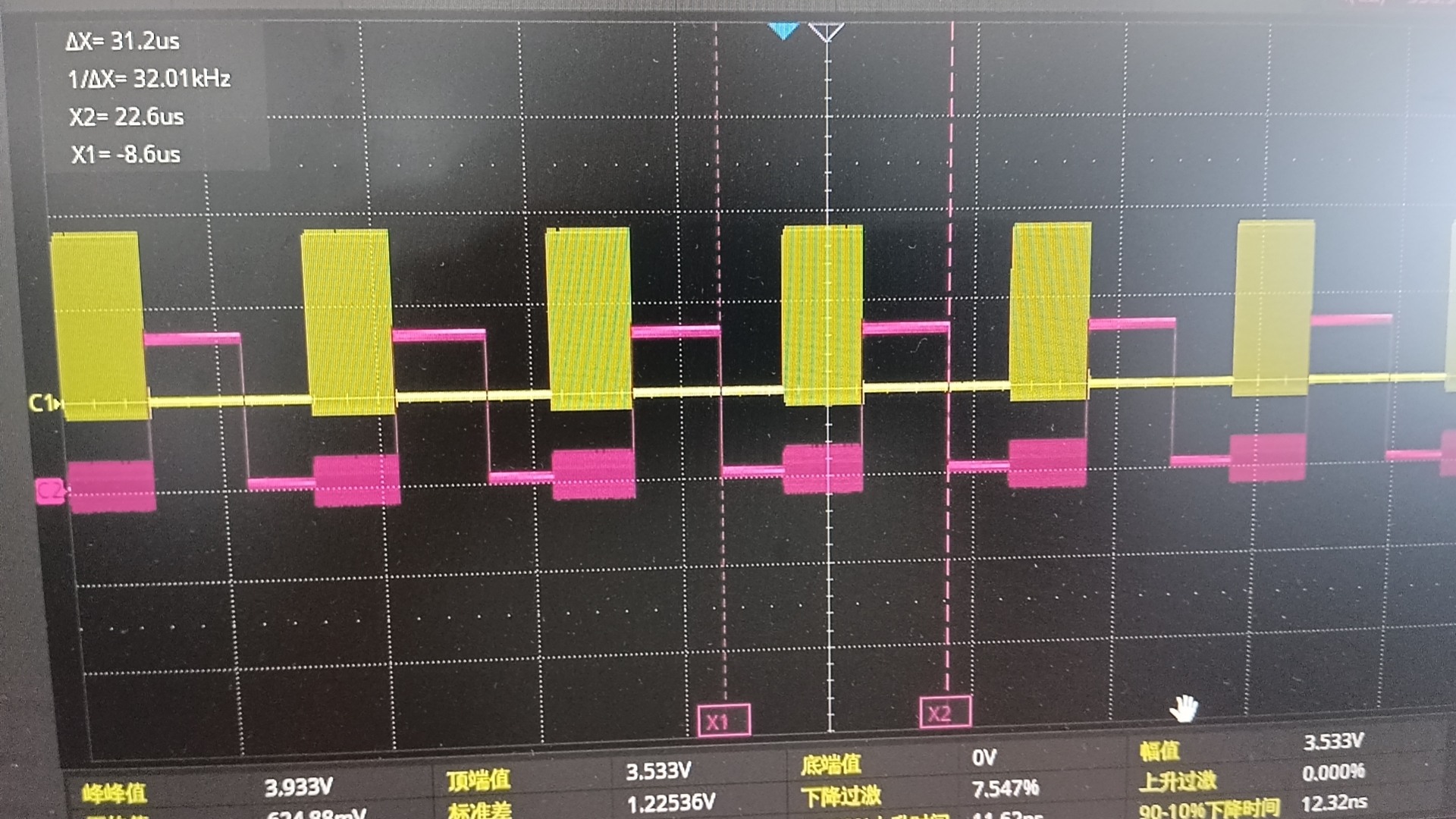

我在读取 ADS131m08时遇到一些问题、我的工程设计和配置是这样的:我使用 STM32H743作为主设备。 SPI 时钟设置为20M、ADS131mM08时钟设置为8.192M。 采样率设置为32KSPS。 设置为 SPI+DMA 模式以与 ADS131M08进行通信、ADS131M08的 DRDY 线路会触发中断以通知 STM32H743读取数据、在 STM32H743的中断功能中启用 DMA 传输、并启用 DMA 中断。 每次读取27个字节的数据(每个字长为24位、总共8个字)、每次启用 DMA 传输数据时、都会确定是否已发送最后一次 DMA。 当启用 DMA 以传输数据时、将标志设置为 false、然后在 DMA 中断函数中将该标志设置为 true、指示读取当前数据。 现在我的问题是 DMA 使用 DRDY 外部中断概率发送障碍无序传输数据。 这意味着有时数据传输会与 DRDY 中断同步、如下面的图1所示。 其中红线为 DRDY、黄线为 SPI CLK、可以看出 DRDY 的周期为32k。 我在程序中记录了 DRDY 中断和 DMA 中断完成的时间、发现这两个计数在1秒内约为32K、两个计数相等。 有时数据传输会出现问题、如下面的图2所示。 DRDY 是红线、因此为什么涡周期的中间会出现脉冲凸点? 此脉冲可能会引起 STM32H43外部中断、因为上面提到的两个计数不再相等、1秒内的 drdy 中断数大约为40K、而 DMA 传输完成中断大约为31K。 造成此问题的原因是什么以及如何解决或避免此问题? 谢谢你。

图1:

图2: