Other Parts Discussed in Thread: ADC12QJ1600

工具与软件:

您好!

我想搭配 ADC12QJ1600 ADC、为 PolarFire FPGA 配置微芯片 JESD204B 内核。

硬件的局限性是我最多只能将4个通道连接到 FPGA。

第一步是 设置 ADC、仅启用一个内核(A)、使其他内核(B、C、D)断电。

如果我选择 JMODE9 (8位、2通道、8B/10B 编码)、应该如何配置 FPGA JESD 内核?

/Mikael

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: ADC12QJ1600

工具与软件:

您好!

我想搭配 ADC12QJ1600 ADC、为 PolarFire FPGA 配置微芯片 JESD204B 内核。

硬件的局限性是我最多只能将4个通道连接到 FPGA。

第一步是 设置 ADC、仅启用一个内核(A)、使其他内核(B、C、D)断电。

如果我选择 JMODE9 (8位、2通道、8B/10B 编码)、应该如何配置 FPGA JESD 内核?

/Mikael

你好、Mikael、

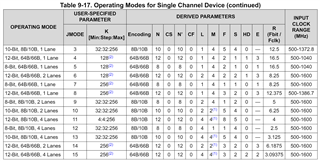

这不是问题、ADC 将在此模式下工作。 要启用该功能、您必须在 ADC 寄存器0x209中启用"single_ch_EN"寄存器、并且从 JESD 的角度来看、您的配置将随通道数的变化而略有不同。 ADC 数据表中有一个部分专门讨论了 ADC 单个通道的 JESD 配置。 请参阅表9-17 (下面的屏幕截图)在其中、您会看到 JMODE9非常相似、但现在它仅适用于 ADC 的单个通道且仅使用两个通道。 请使用这些 JESD 参数来配置 FPGA。

此致!

Eric

您好!

因此、我根据您的建议将 ADC 配置为单核。

和 FPGA 内核计算如下:

采样频率1500MHz 基于 SE_CLK 和 PLLREFO 输出上的50MHz XO、为 FPGA 提供相同的参考时钟。

SYNC 引脚用于同步。

未使用 SYSREF 和 TMSTP 输入。

器件是根据数据表第10.3节中定义的顺序设置的。

我正在监视由 FPGA 内核生成的 SYNCSE 信号、我预期该信号会 先低电 平再高电平、但它卡在低电平。

ADC 的一些状态寄存器读数(如果您想查看其他寄存器、请告诉我):

JESD_STATUS (0x208)- 0x01

INIT_STATUS (0x270)- 0x01

VCO_CAL_STATUS (0x5E)- 0x03

CAL_STATUS (0x6A)- 0x0C

ALARM_STATUS (0x2C1)- 0x08 (启动时清除位后)

似乎无法通过同步步骤??

为什么 SPLL_LOCKED 未处于活动状态? 它是否基于 根据 JESD_STATUS 寄存器锁定的 CPLL?

谢谢!

此致

Mikael

你好、Mikael、

您能否确认您使用的是 ADC EVM 还是定制电路板?

是的、SPLL 应该锁定、它源自器件时钟、在这种情况下、该时钟来自 CPLL。 在对 FPGA 进行编程之前、您可以读取 JESD_STATUS 寄存器(0x208)的值。

您将遇到的另一个问题是、从 ADC 到 FPGA 的时钟输出可能是与 FW 所期望的频率不同的频率、您是否能够与 JESD 内核时钟共享 XCVR 参考时钟应该是的频率以及 JESD 内核时钟应该是什么? 上述任何一项都不正确都会导致链接挂起。

谢谢!

Eric

您能否确认您使用的是 ADC EVM 还是定制电路板?

这是定制板。

[报价 userid="566984" url="~/support/data-converters-group/data-converters/f/data-converters-forum/1371018/adc12qj1600-microchip-polarfire-fpga-jesd204b-configuration/5245984 #5245984"]是的、SPLL 应该锁定、它源自器件时钟、在本例中源自 CPLL。 在对 FPGA 进行编程之前、您可以读取 JESD_STATUS 寄存器(0x208)的值。[/QUOT]ADC 器件引脚:

PD -高电平(器件上电)

PLL_EN—高电平

PLLREF_SE—高电平

SYNCSE -低

CALTRIG -低

CLKCFG[0..1]-低电平

在任何 ADC SPI 配置之前读取 JESD_STATUS (FPGA 仍处于编程状态):

JESD_STATUS (0x208)- 0x05

我的 SPI 配置可能有什么问题(由于 SPLL 在上电时锁定)吗?

您会遇到的另一个问题是、从 ADC 到 FPGA 的时钟输出可能与固件预期的频率不同、您能否分享 XCVR 参考时钟以及 JESD 内核时钟应该是什么? 其中任何一个错误都将导致链接挂起。

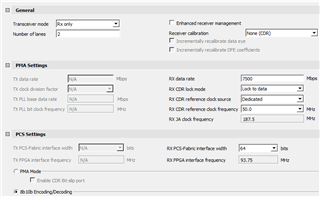

我在下面发布了收发器内核的配置页面:

/Mikael

你好、Mikael、

JESD_STATUS 为0x05很好、这表示 cpll 和 spll 都正在锁定、但也表示 ADC 的 SYNC 保持低电平、这表明存在 FPGA FW 问题。

您的问题是、对于 RX 结构时钟、时钟设置为 SerDes/80、对于 RX JA 时钟、时钟设置为 SerDes/40。 您能否确认如何将这些参考时钟生成到 FPGA。 我猜这些是错的。

此致!

Eric

这是一种误解。

JESD 状态仍为0x01、因此 S-PLL 未锁定、只有 C-PLL。

这对我来说是一个谜! 我看不到 S-PLL 锁为什么 会失败?

[报价 userid="566984" url="~/support/data-converters-group/data-converters/f/data-converters-forum/1371018/adc12qj1600-microchip-polarfire-fpga-jesd204b-configuration/5260842 #5260842"]您认为、对于 RX 结构时钟、时钟的时钟设置为 SerDes/80、对于 RX JA 时钟、时钟的时钟设置为 SerDes/40。 您能否确认如何将这些参考时钟生成到 FPGA。 我猜这些是错误的。我将 SE_CLK 输入与50 MHz XO 配合使用、

它用作 C_PLL 的基准以生成7500 MHz 采样时钟。

50 MHz XO 还通过 PLLREFO 输出路由到 FPGA、并在 FPGA IP 内核配置中用作"RX CDR 参考时钟"。

FPGA IP 内核设置:

"RX JA 时钟频率"是根据设置为7500的"RX 数据速率"自动计算的。

"RX JA 时钟频率"是否必须与"RX FPGA 接口频率"匹配? 我想不是吗?

此致

Mikael

你好、Mikael、

如果您只启动 ADC 而不使用 FPGA、则应锁定 SPLL。 如果链路未能接通、这也将是低电平。

我不确定生成7500 MHz 采样时钟的意思、我想您在引用该器件中的 VCO。 这分为该器件的实际时钟速率、最大值为1.6GHz

RX 数据速率应为 SerDes 链路的线速率、在此模式下可计算为 FS*R

其他两个时钟具有不同用途。 一个将用作参考时钟、将 FPGA 内部的 PLL 锁定到链路的线路速率、另一个将用作 JESD 内核时钟。 我不熟悉 microfire IP 的配置和设计如何工作、因此您必须跟他们跟进、以准确了解比率应该是多少。 通常、对于8b10b 模式、核心时钟的一些默认值为线速率/40或线速率/80。

此致!

Eric