工具与软件:

嗨、团队:

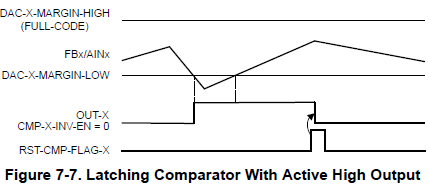

我的客户考虑使用具有高电平有效输出的可编程迟滞比较器模式和锁存比较器。 请查看数据表上的图7-7。 在此模式下、当 FBx/AINx 降低 DAC-X-MARGIN-LOW 且 RST-CMP-FLAG-X 变为高电平时、OUT-X 是否会继续保持高电平? 在图7-7中、OUT-X 会变为低电平、因为 FBx/AINx 高于 DAC-X-MARGIN-LOW 且 RST-CMP-FLAG-X 变为高电平、但当 FBx/AINx 低于 DAC-X-MARGIN-LOW 且 RST-CMP-FLAG-X 变为高电平时会发生什么情况?

此致、

山本俊介