工具与软件:

您好!

我想将此 ADC 的 LVDS 差分 O/PS 连接到使用 HP IO 组的 Virtex Ultrascale Plus FPGA。

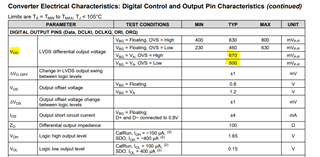

下面是来自 ADC 数据表。

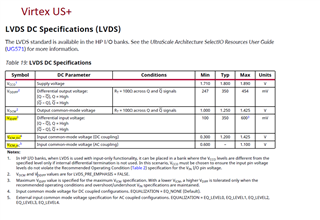

下面是 Virtex UltraScale FPGA HP IO 组特性(链接):表19

1. 交流和直流耦合的差分 ADC 输出的共模电压是多少? 它是否与上面突出显示的 FPGA 接收器特性匹配?

2.根据 FPGA 产品说明书、FPGA 的差动模式规格 最大为600mV。 这是不是一个与 ADC 输出集成的问题?

我们之前已在使用同一 ADC 的较旧设计中使用了 Virtex6、但未发现任何问题。 但是、由于我们要开发新的 FPGA、因此我们需要确保这一点。

谢谢。