工具与软件:

团队成员、您好!

我的客户对时钟和转换计时有几个问题。

是否可以回答以下问题?

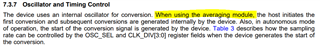

1.当客户是时 不会 使用均值滤波器时 、它们是否可以忽略 OSC_SEL 和 CLK_DIV[3:0]设置? 它们似乎仅用于取平均值模块。

2.手动模式优于动态模式有哪些优点或用例? 由于通道选择没有延迟、动态模式似乎更好。

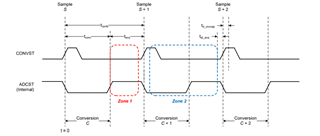

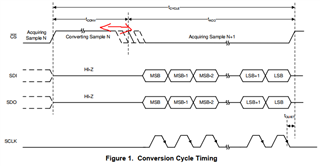

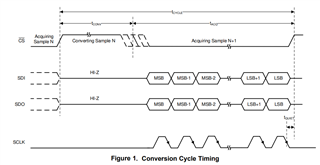

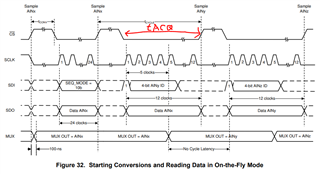

3.图1 (转换周期时序)意味着什么?

这是否意味着用户必须将 CS 拉为高电平才能启动转换、必须手动将 CS 拉为低电平才能开始采样?

或者是否会在转换完成时自动启动 Acquisition (采集)。 它会通过 ADC 拉取 CS 吗?

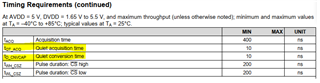

4.产品说明书中的 Tacq 为400ns (最小值)。

当使用 SPI 的50MHz 时、12个时钟将为240ns、因此似乎无法实现400ns 的 Tacq。

这是真的吗?

5.什么是静默采集时间和静默转换时间? 我从数据表中找不到任何解释。

此致、

Kei Kuwahara