Other Parts Discussed in Thread: DAC39J82EVM, LMK04828

主题中讨论的其他器件: LMK04828

工具与软件:

您好!

我正在尝试将 DAC39J82EVM 与 ZCU102电路板一起使用、对其进行设置时遇到了很多困难。 我特别请求并收到了 TI-JESD IP、该 IP 随附 ZCU102参考设计、我将尝试实施该设计。 参考顶部设计有4个需要连接的时钟信号、该参考设计附带的限制文件分配了以下引脚:

| 时钟信号 | 引脚名称 | FMC 引脚 | DAC3XJ8XEVM 原理图 |

| sys_clk_p | CLK1_M2C_P | G2. | 未分配 |

| REFCLK_p | GBTCLK0_M2C_C_P | D4 | GTX_CLKP |

| sysref_p | LA22_P | G24 | 未分配 |

| tx_sync_n | LA26_P | D26. | 未分配 |

现在、如果我正确理解这些时钟的工作原理:

- sys_clk_p 应路由到频率为 LineRate/80的时钟(对于我的 data_width=64)。 我假设在 DAC 原理图上、它应该连接到 FMC_DACCLK_P、因此 FMC 引脚 D8。 知道线性速率后、我需要修改参考设计中存在的时钟向导、以便匹配此时钟的频率与所需的生成时钟。

- 我认为 REFCLK_p 已正确路由至 GTX_CLKP

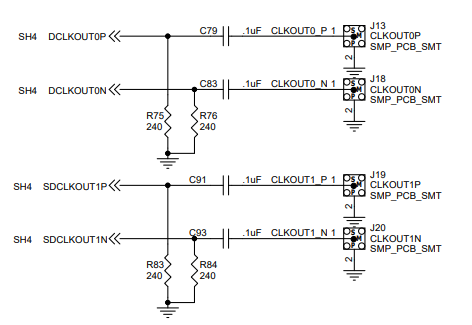

- 我理解的 sysref_p 应该连接到对应于 FMC 引脚 D11的 FMC_SYSREF_P

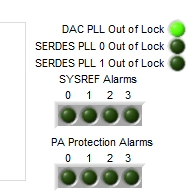

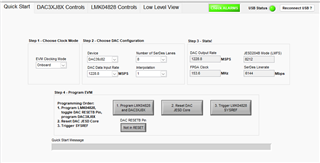

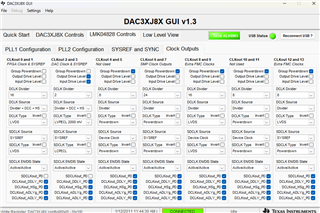

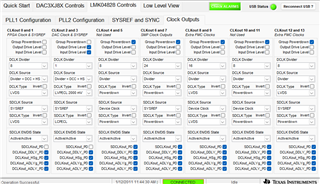

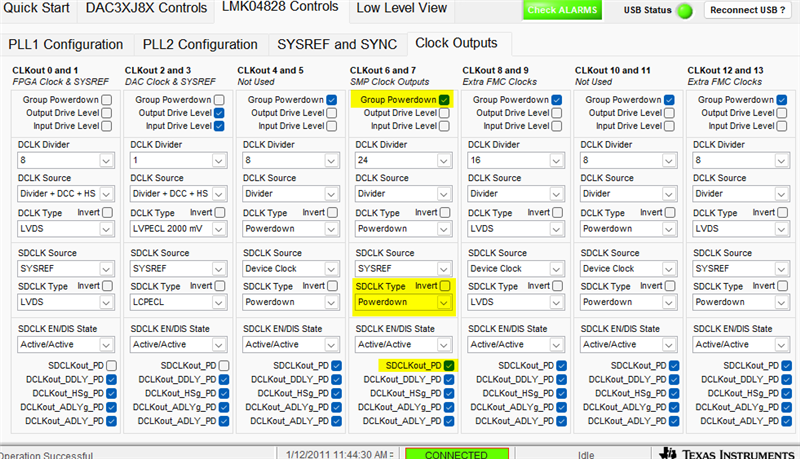

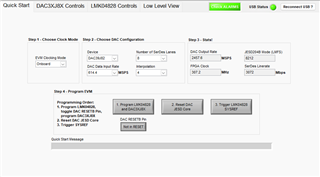

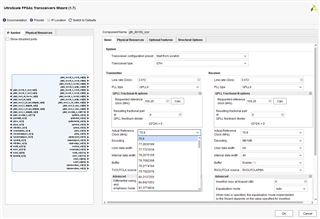

考虑到这一点、我使用以下参数来设置 GUI

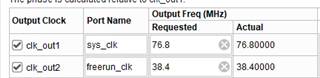

这意味着 sys_clk 时钟应该具有38.4 MHz 的频率、因此我会在时钟向导中将其设置为输入频率。 此外、当我在收发器向导中设置参数时、我可以为实际参考时钟设置的最小频率是76.8 MHz、而不是38.4 MHz、我假设它对应于使用计时向导从 DAC 板生成的 sys_clk_p (n)对中生成的 sys_clk。

另一方面、在"Physical Resources"选项卡中、自由运行时钟频率设置为38.4 MHz 的最大值、我假设这应该与设置的频率与时钟向导的 freerun_clk 输出相匹配。 在时钟向导中、使用这两个值、我将 sys_clk 频率设置为76.8、将 freerun_clk 设置为38.4。

我为 sys_clk 和 sysref 添加了2个调试信号以从 ZCU102中提取一些 PMOD、而且对于我提到的配置、我只能看到噪声。 如果我尝试将引脚修改为正确的引脚、Vivado 会导致错误[放置30-681]、无法实现支持时钟的引脚和 MMCM 对的理想放置。 对此有什么想法吗?

谢谢!

Matías μ A。