Other Parts Discussed in Thread: ADS54J69, ADS54J60

主题中讨论的其他器件: ADS54J60

您好!

我们正在尝试在定制 FMC 板上配置 ADS54J69。 通过示波器、我们可以看到数据从 FPGA 进入 SDIN 线路上的 ADC、我们可以看到 SCLK 上的正确 SPI 时钟、并且我们的复位线路的行为正常。

然而、我们是 SDout 上没有任何数据 这告诉我们 ADC 无响应 .

我们将这些值写入寄存器以将 ADC 设置为 LMFS-4211:

// FMC231 ADS54J60设置

// LMFS = 4211、无抽取模式。 该模式仅适用于 ADS54J60。 JESD204通道0 = DA1;通道1 = DA2

静态 SPI_BUS_t ads54j60_4211_init_regs[]=

{

//寄存器写入复位

{{0x00、0x00}、0x81}、//复位模拟组的 ADC 和主页面中的寄存器。

{{0x40、0x01}、0x00}、//清除 JESD 组未使用的页面中任何不需要的内容。

{{0x40、0x02}、0x00}、//清除 JESD 组未使用的页面中任何不需要的内容。

{{0x40、0x03}、0x00}、//选择 JESD 组的主数字页面。

{{0x40、0x04}、0x68}、//选择 JESD 组的主数字页面。

{{0x60、0xF7}、0x01}、//使用 DIG RESET 寄存器位复位 JESD 组中的所有页面。

{{0x60、0x00}、0x01}、//设置通道 A 的脉冲复位寄存器位

{{0x60、0x00}、0x00}、//通道 A 的 Cler pulse reset 寄存器位

//性能模式

{{0x00、0x11}、0x80}、//选择模拟组的主页。

{{0x00、0x59}、0x20}、//设置始终写入1位。

//选择 JESD 数字页面

{{0x40、0x04}、0x69}、//选择 JESD 数字页面

{{0x40、0x03}、0x00}、//选择 JESD 数字页面

//选择 CTRL K 位

{{0x60、0x00}、0x80}、//稍后根据序列中的 SYSREF 信号对 K 进行编程、以设置两个通道的 CTRL K 位。

//启用扰频

{{0x60、0x05}、0x80}、

// K=32

{{0x60、0x06}、0x1F}、//每帧成名帧数

//选择数字到40x 模式

{{0x60、0x01}、0x04}、//四个通道处于活动状态、无抽取(滤波器旁路)、将 SYNC 引脚用于同步请求、正常运行

//或测试模式

//{{0x60}、{0x01}}、{0x84}//四个通道处于活动状态、无抽取(滤波器旁路)、对同步请求使用 SYNC REG 寄存器位、ADC 输出数据替换为 K28.5字符。

//选择 JESD 模拟页面

{{0x40、0x04}、0x6A}、

{{0x40、0x03}、0x00}、

//将 SERDES PLL 设置为40x 模式

{{0x60、0x16}、0x02}、

// PLL 复位

{{0x60、0x17}、0x40}、// PLL 复位设置

{{0x60、0x17}、0x00}、// PLL 复位清除

/*//发送器幅度

{{0x60、0x1B}、0x60}、//[7:5] JESD 摆幅。 0= 860mV 1=810 2=770 3=745 4=960 5=930 6=905 7=880 [3] FOVR 通道

//去加重

{{0x60、0x12}、0x04}、//[7:2]去加重0=0dB;1=-1 3=-2 7=-4.1 F=-6.2;1F=-8.2 3F=-11.5

{{0x60、0x13}、0x04}、

{{0x60、0x14}、0x04}、

{{0x60、0x15}、0x04}、

*/

//选择主数字页面

{{0x40、0x04}、0x68}、

{{0x40、0x03}、0x00}、

//对脉冲复位寄存器位进行脉冲处理

{{0x60、0x00}、0x01}、//脉动脉冲复位寄存器位。 主数字页中编程的所有设置只有在该位脉冲后才会生效。

{{0x60、0x00}、0x00}、//脉动脉冲复位寄存器位。 主数字页中编程的所有设置只有在该位脉冲后才会生效。

{{0x00、0x00}、0x00}//最后一个

};

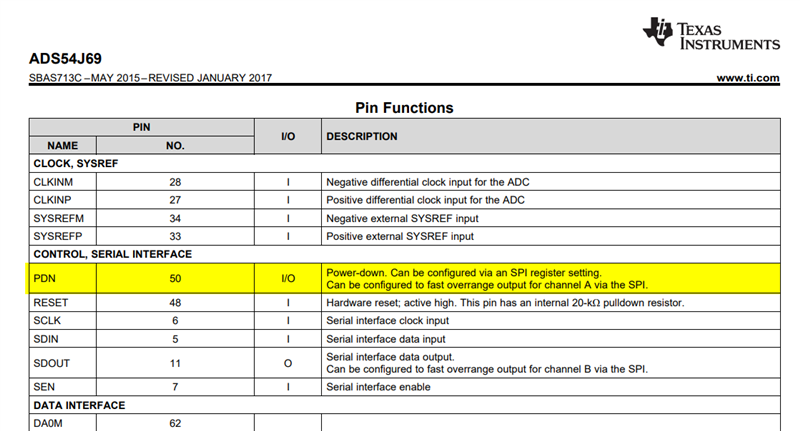

在我们的设计中、我们的 PDN 引脚连接至高电平、我们的上述固件和 SPI 设置不能寻址此引脚、我们不打算使用断电模式。

是否可以检查上述设置、以及是否需要对 PDN 引脚执行任何操作?

谢谢!

Ryan