工具与软件:

您好、

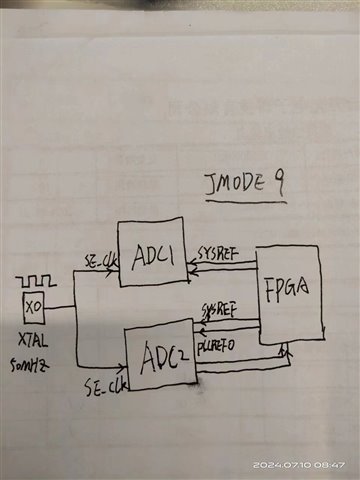

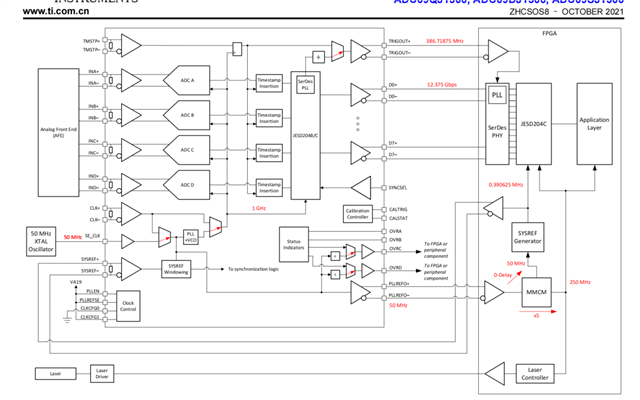

该项目基于 jesd204b 协议、以实现两次 ad09qj1300数据传输、使用外部50MHz 晶体振荡器作为时钟输入、AD 采样率=1G、JMODE=10和子类1模式。

jesd204b phy 的 REFCLK 使用195.3125 MHz 处 ADC 的 trigout 伴随时钟(R/32)、core_clk 是 ADC 的50 MHz 基准时钟、其乘以156.25 MHz (R/40)、并通过除以参考时钟获得 sysref 时钟(195.3125kHz)。 在链路建立过程中、存在以下问题:

1.我们的板(同一块板上有两个 ADC 芯片)回来进行加电测试、发现有两种默认的 ADC 功耗情况。 后来、该程序读取发现电路板上低功耗 ADC 的 S-PLL 未锁定。 正常程序配置后、所有 ADC 再次恢复正常。 使用不同默认 ADC 状态的原因是什么。

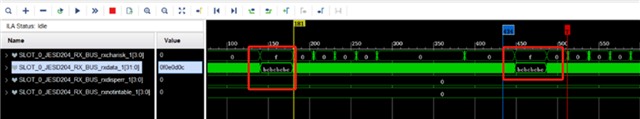

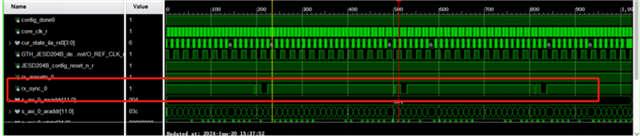

2.当0x207='h02 (K28.5)且0x205='h04 (RAMP)时、SYNC 成功提升。 但是、当修改0x205='h05 (短传输)时、SYNC 会失去锁定并出现周期性变化。 jesd204b 寄存器显示收到意外的 K 代码、如下图所示:

修改0x207='h01 (K28.1)后、在不同的测试模式下、同步成功且稳定地提升了电平。 为什么 K28.5和 K28.1导致不同的现象? 为什么会有这样的差异?

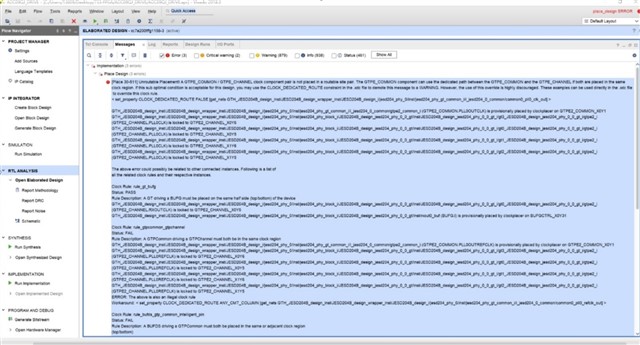

3.在 FPGA 中为 GTP 专用时钟和数据引脚分配引脚时应注意什么? 由于两个组中的时钟多路复用、同一组中的数据引脚是否必须被分配到同一组? 请提供详细信息、说明分配不当时可能会出现以下错误:

谢谢!