工具与软件:

团队成员、您好!

客户在设计 ADS1014-Q1时遇到了一些问题、需要与您确认以下问题:

1.什么是 ADC 采样频率一半的具体范围;

2.什么是 不需要的信号, 什么是范围?

3. fmod /2的含义和价值是什么?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

团队成员、您好!

客户在设计 ADS1014-Q1时遇到了一些问题、需要与您确认以下问题:

1.什么是 ADC 采样频率一半的具体范围;

2.什么是 不需要的信号, 什么是范围?

3. fmod /2的含义和价值是什么?

谢谢!

Daniel、您好!

感谢您的提问!

Unknown 说:1. ADC 采样频率一半的具体范围是多少;

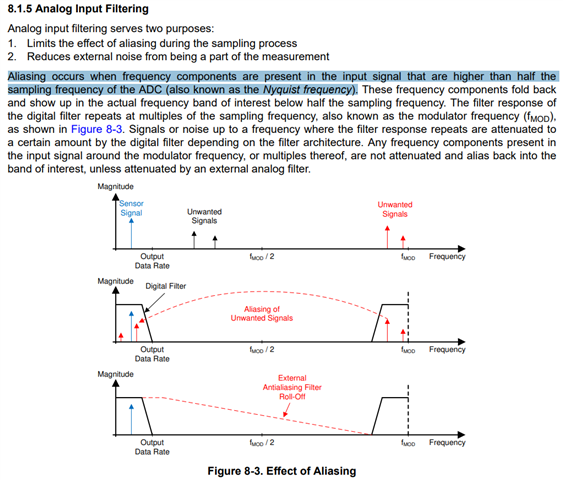

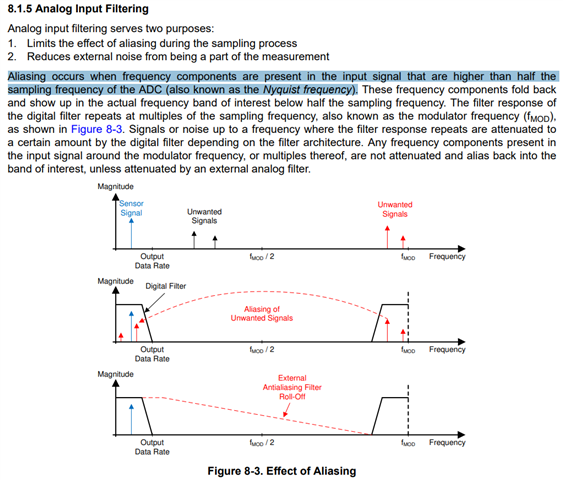

这将与客户使用的数据速率有关、奈奎斯特标准要求采样频率必须至少是输入信号最高频率的两倍、否则信号信息将丢失。

例如、 128sps ADC 输出速率会将输入限制为64Hz。

Unknown 说:2. 无用信号的含义是什么、 范围是什么?[/QUOT]无用信号将指在传感器信号之外拾取的任何信号。 潜在的不需要的信号可能会出现混叠、传感器接线拾取的内部噪声、或者电磁干扰(EMI)或射频干扰(RFI)产生的外部噪声。

如果采样频率小于最大输入信号频率混叠的两倍、则会产生不必要的信号。 在大多数情况下、可通过在模拟输入上使用一阶电阻电容(RC)滤波器来减少混叠。

Unknown 说:3. fmod /2的含义和价值是什么?根据 第7.3.2节 如下数据手册:对输入信号进行采样的频率称为采样频率或调制器频率(fmod)。 fmod = 250kHz、fmod / 2将等于125kHz。

Δ-Σ ADC 基于过采样原理构建而成、在该原理中、Δ-Σ 调制器会对多个读数求平均值并输出其平均结果。 根据此原理、Δ-Σ ADC 的输出数据速率通常比频率 fmod 的输出数据速率低数百倍。

此致、

Andrew

[/quote]