请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC3664 工具与软件:

尊敬的技术支持团队:

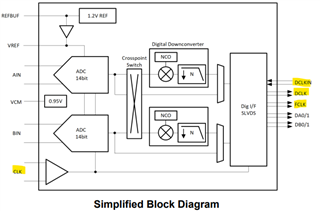

我想在同一块板上使用六个 ADC3664、它有四个 CLK。

您对减少或共享时钟有什么想法吗?

CLK (输入)

DCLKIN (IN)

DCLK (输出)

FCLK (输出)

根据之前的帖子、它似乎减少了并共享了时钟。

是这样吗?

此致、

TTD

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TTD:

TI 可能有一个时钟器件可用于驱动所有6个器件的采样时钟和 DCLKIN。 如果您需要这方面的更多信息、请告诉我。

但您仍需要将所有这些时钟路由到六个 ADC 中的每一个。

对于 DCLKOUT 和 FCLK、遗憾的是您需要将它们中的每一个从每个 ADC 带到 FPGA。

您是否研究过我们的一款四通道或八通道器件、它们在这方面可能有助于减少时钟要求数量?

谢谢!

Rob