主题中讨论的其他器件: ADS8584S、

工具与软件:

尊敬的技术支持团队:

我对 ADS8588S 和 ADS8584S 有疑问。

问题1

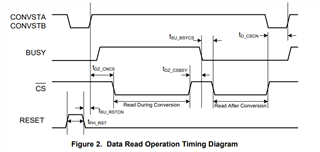

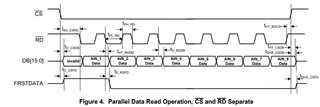

ADS8588S 配备了8通道 ADC、但当在转换后仅读取4个通道(CH1至 CH4)时、仅将"CONVSTA"置为"1"并使用"图2"。 数据读取操作时序图"和‘图4:并行数据读取操作、CS 和 RD 分离"。 (CONVSTB 固定为"0"、未使用)

是这样吗?

问题2

如果我只读取 Q10的4个通道、ADS8588的 tCONV (转换时间)是否需要3.7至3.9us?

由于 ADS8584的 tCONV 是2us (典型值)、我想知道是否可以缩短该时间。

问题3

如果将 ADS8588SEVM-PDK 中安装的 ADS8588S 替换为 ADS8584S、除了从8个通道减少到4个通道之外、是否有其他问题?

例如、电路板上 J9连接器引脚的引脚分配是否有任何变化、或者是否有任何引脚不再使用?

此致、

TTD