Other Parts Discussed in Thread: ADS127L21

工具与软件:

您好!

我对 ADS127L21有几个问题。

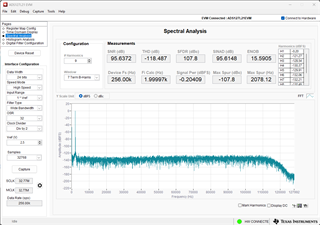

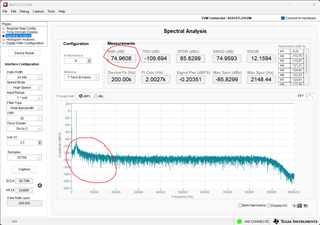

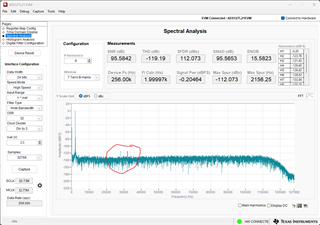

1)在评估板数据表和 ADS127L21数据表中是否指出不建议使用内部时钟进行交流电压测量。 但我们使用500mV 交流单极信号和1.65V 直流失调电压、使用评估板对其进行了测试。 我们已读出此信号。 在什么情况下该表达式对交流电压有效。 在测量1.65VDC 偏移和500mVAC 信号时、我们是否会使用内部时钟遇到任何意外的 ADC 交流电压测量问题。

2) 2) 向 ADC 应用外部时钟时、我们是否需要测量时钟? SCLK 和外部时钟是否需要同步? 由于数据表说明了以下内容:"减小 SCLK 和 CLK 之间的相位偏斜(< 5ns)"。 我没有完全理解这句话、原因是什么?

我希望能迅速作出答复。

谢谢你