工具与软件:

我将一个 ADC 以串行模式连接到我的电路、完全通电。 当硬件模式激活时、我将从 ADC 获得有效响应和通信。 当我以软件模式将 HW_SW 引脚驱动为高电平时、不会从 ADC 接收到 BUSY 信号的初始脉冲、也不会在 SCLK 的32个时钟周期之后在 BUSY 引脚取消置位并使 FS 生效后接收到脉冲。 我正按照下面所示的确切顺序操作、但从不会收到 BUSY 发出的响应。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

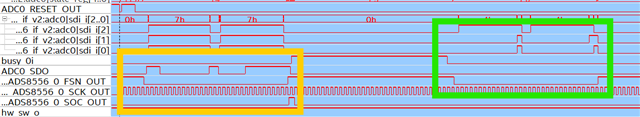

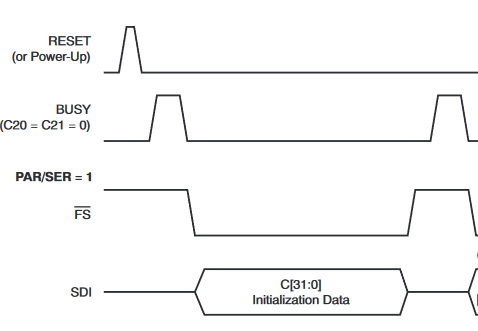

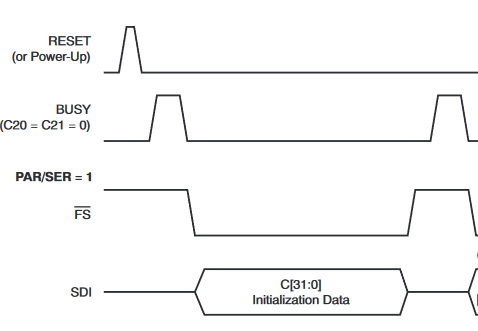

我将一个 ADC 以串行模式连接到我的电路、完全通电。 当硬件模式激活时、我将从 ADC 获得有效响应和通信。 当我以软件模式将 HW_SW 引脚驱动为高电平时、不会从 ADC 接收到 BUSY 信号的初始脉冲、也不会在 SCLK 的32个时钟周期之后在 BUSY 引脚取消置位并使 FS 生效后接收到脉冲。 我正按照下面所示的确切顺序操作、但从不会收到 BUSY 发出的响应。

Jonathan、您好!

感谢您的分享。 您是否可以尝试切换复位引脚? 读取 此 E2E 线程、有时启动时的 POR 有时可能不会完全复位器件、也看不到 BUSY 信号、但 RESET 引脚切换可以解决此问题。 注意、复位脉冲长度必须至少为50ns。

如果这样无法解决该问题、那么在使用 SDI 设置初始化寄存器后、您会看到什么行为? 此外、您是将 TI EVM 用于此评估还是使用您自己的电路板? 如果使用您自己的电路板、您能否提供原理图以便我也能看一下?

此致!

Samiha

Jonathan、您好!

看看您的/SDI 信号、假设 FS 数据正在由 ADC 计时输入、在您的屏幕截图中看起来像是 CR[31:29]全部为零(默认情况下)、因此所有3个通道对都在下一次转换时被禁用。 您能否尝试将其设置为1以启用它们、看看这是否有什么不同?

您的原理图看起来不错、尽管看起来好像在 AVDD 上缺少去耦电容器。 此外、根据数据表、您是否可以在软件模式下以串行模式尝试将引脚63连接到 GND?

您也可以尝试设置 C17 = 1来尝试查看 CR 寄存器的内容。

当前 SDO (ADC 输出)包含哪些内容?

此致、

Samiha

Jonathan、您好!

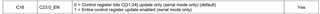

我懂了。 C21应该为0、因为我们希望 BUSY/INT 引脚用作 BUSY 引脚。 另请注意、C16应设置为1以更新 C[0:23]。

设置 C21=0、C[31:29]= 1并且 在 SCLK 的32个时钟周期后切换 FS 之后、您可以尝试切换 CONVST 吗?

此外、XCLK (引脚27)连接到什么? 如果未使用此引脚、则应将其连接到 BVDD 或 BGND。

您能否使用示波器来验证您的 HVDD、HVSS、AVDD 和 BVDD 电压? ADC 输入端的电压是多少?

此致、

Samiha

尊敬的 Samiha:

对不起,我没有在上面的帖子提到它,但是的 C[31:29]=1。 C[17:16]= 1和 C[9:0]= 1通过 ADC0_SDO 信号发送到 ADC、如黄色框中所示。 在32个 SCLK 周期之后、我使 FSN 有效并发出 CONVST 信号(SOC_O)脉冲。 在绿色框中、BUSY 信号变为低电平之后、我会将 FSN 降至0并持续32个 SCLK 周期、以便读取寄存器。 串行数据线(SDI_I)返回的数据与我所期望的数据不匹配。 返回值不应该与寄存器设置匹配吗?