工具与软件:

您好!

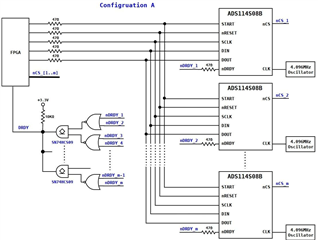

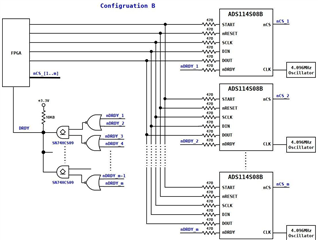

我目前正在设计一个多通道加热系统、该系统将利用 FPGA 与多个 ADS114S08B 器件连接、以进行4线 RTD 测量。 为了优化 FPGA 信号线的数量、我计划使用单个 SPI 总线连接多个 ADS114S08B 器件。 我对这种设置有几个问题:

1.数据表(第10.1.1节)建议将一个47欧姆电阻与数字输入和输出信号串联。 在所示的两种电阻配置中、哪一种更合适? 或者、您是否会推荐更好的连接方法?

2.同一 SPI 总线上最多可并联的 ADS114S08B 器件数量是多少?

3.使用内部时钟信号还是外部4.096MHz 时钟信号的选择是否会影响获得的 RTD 电阻值的准确性?

4.在随附的图中、连接 DRDY 信号、以便在 FPGA 发送 START/SYNC 信号后、只需检查 DRDY 是否为1即可确保所有 ADS114S08B 器件均已完成转换并准备好进行数据读取。

感谢您的帮助。

此致、