主题中讨论的其他器件:TSW14J57EVM、

工具与软件:

您好!

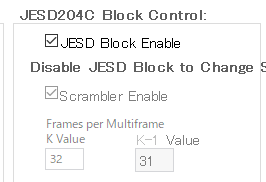

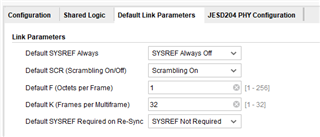

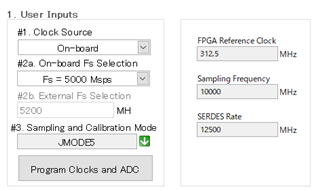

我正在尝试检查 JMODE5的运行情况、并遇到问题。

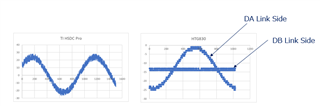

配置1能够捕获从函数发生器到 INA 的正弦波输入。

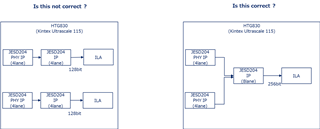

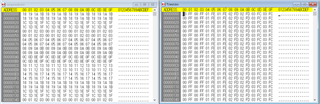

配置2能够捕获 DA 链路端数据的正弦波、但 DB 链路端数据无法捕获正弦波。

当正弦波输入到 INB 时、DB 链路侧的数据能够捕获正弦波、但 DA 链路侧无法捕获正弦波。

过去是否有类似问题的报道?

两个 RX PHY 是否不同步? 我尝试了一个 PHY (8个通道)作为测试、但 DB 端的数据不是正弦、因此我不认为这是同步问题。

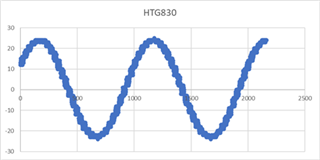

ILA 从 Xilinx 的 JESD204 IP 输出信号采集的数据色图。

在斜坡模式或传输层测试模式下、两个链路似乎都正确存储数据。

测试配置1

TSW14J57EVM (Reve)+ ADC12DJ5200RFEVM

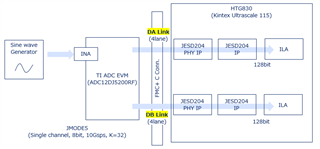

测试配置2

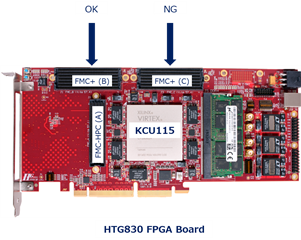

HTG830 (Hitech Global)+ ADC12DJ5200RFEVM

此致、

Takeo