Thread 中讨论的其他器件: OPA388

工具与软件:

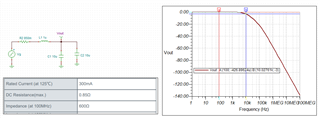

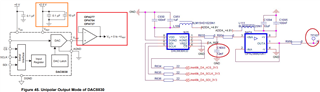

我选择了 DAC8830来实现200Hz 至48kHz 范围内的模拟信号输出。 采样率为153.6kHz。 该电路是根据官方网站文档 TIDA01402中提供的电路图设计的。 实际电路如下图所示。

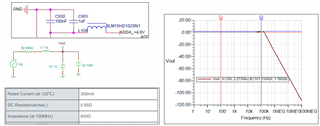

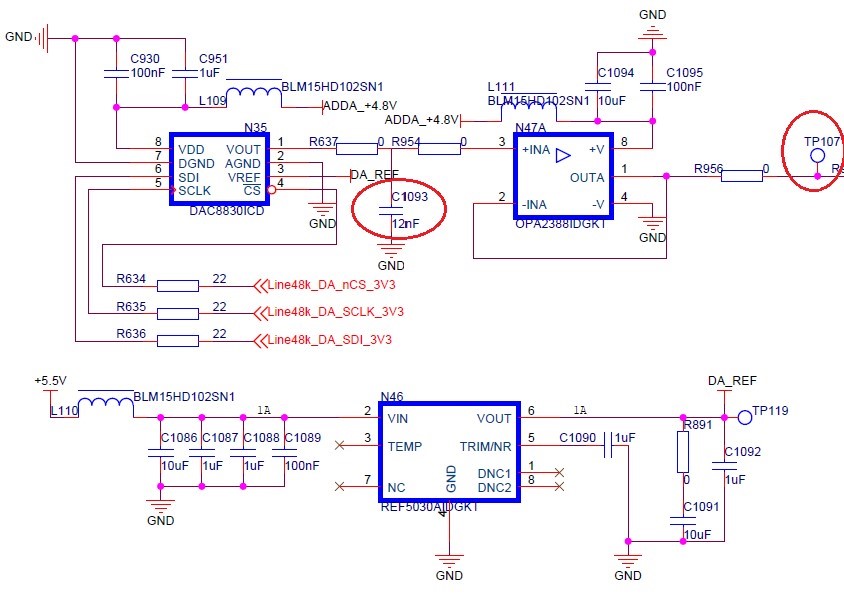

测试电路时、我使用 FPGA 平台上的 IP 内核生成频率为1kHz、振幅为1Vrms 的正弦数字序列。 然后、该信号被发送 到 DAC8830。 我在测试点 TP107测量模拟信号(后级电路断开)。 测得的输出信号频谱如下图所示。 本底噪声基本上低于-100dBV。 信号质量是可以接受的。

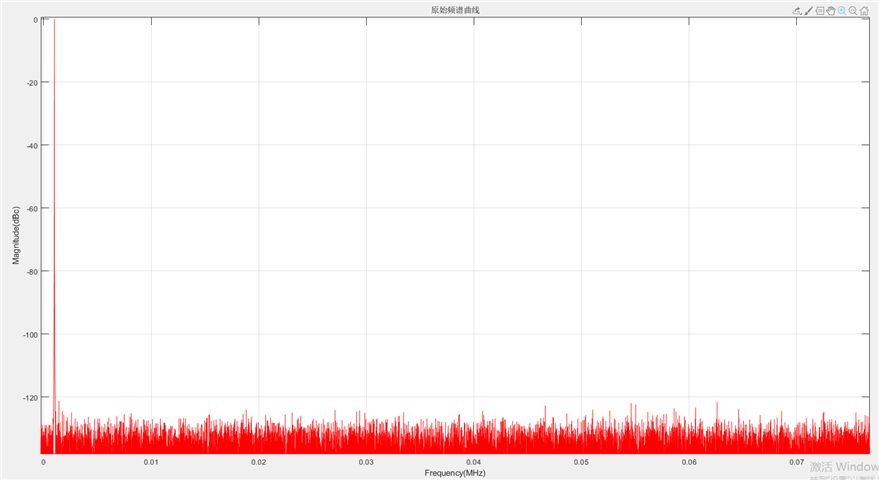

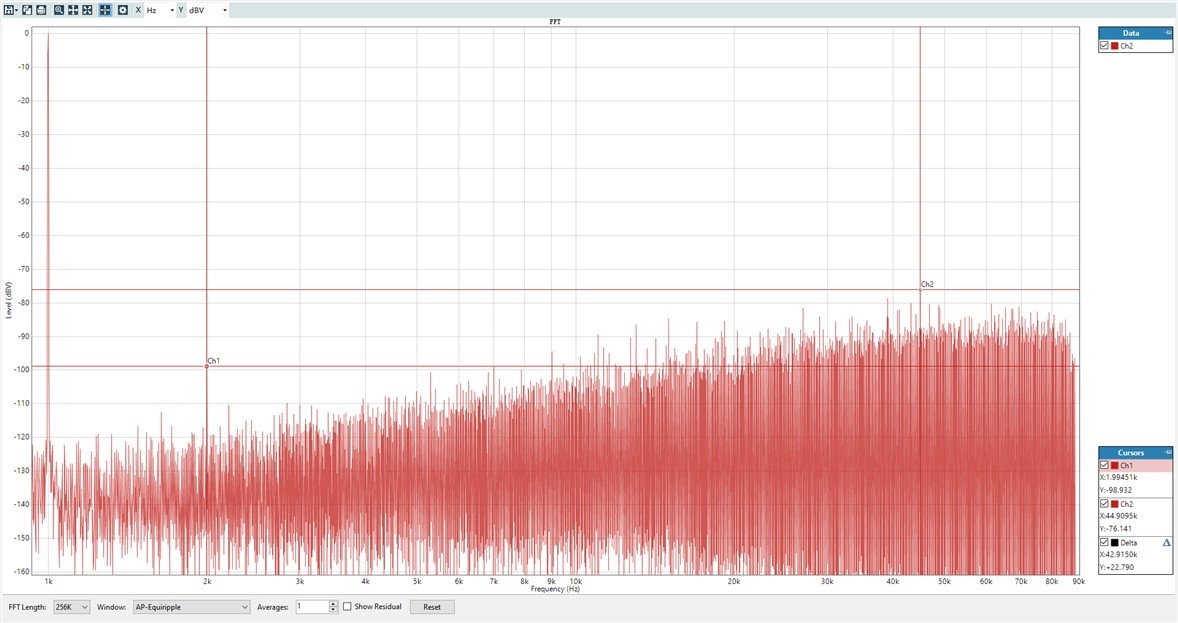

但是、由于信号带宽达到48kHz、因此必须调整电路中 C1093的电容值。 在 TIDA01402文档的电路中、选择了12nF 的电容值。 根据 DAC8830数据表中给出的6.25 kΩ 输出阻抗、截止频率应约为2.1kHz、这无法满足使用要求。 将 C1093的电容值更改为340 pF 会导致一个大约75kHz 的截止频率。 更改电容值后、 频率为1kHz 且振幅为1Vrms 的正弦数字序列仍用作测试信号。 在 TP107测量的信号频谱如下所示。 随着频率的增加、本底噪声也会上升。 奈奎斯特频率内的最高本底噪声达到80dBV。 这与数据表中描述的10nV/√Hz 噪声技术规格有很大不同。

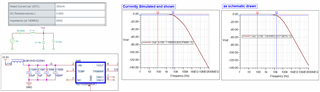

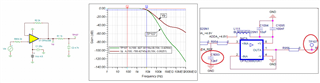

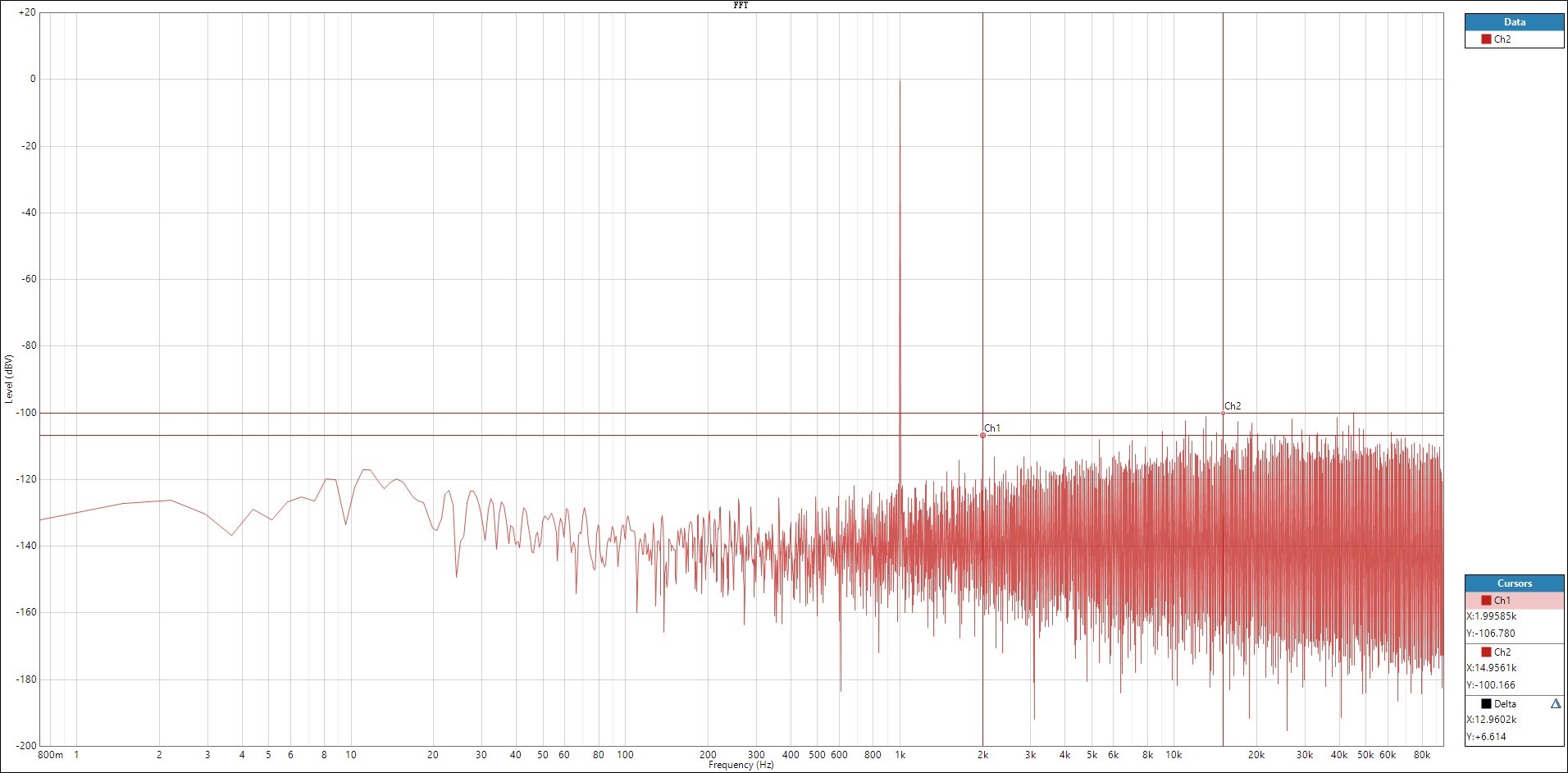

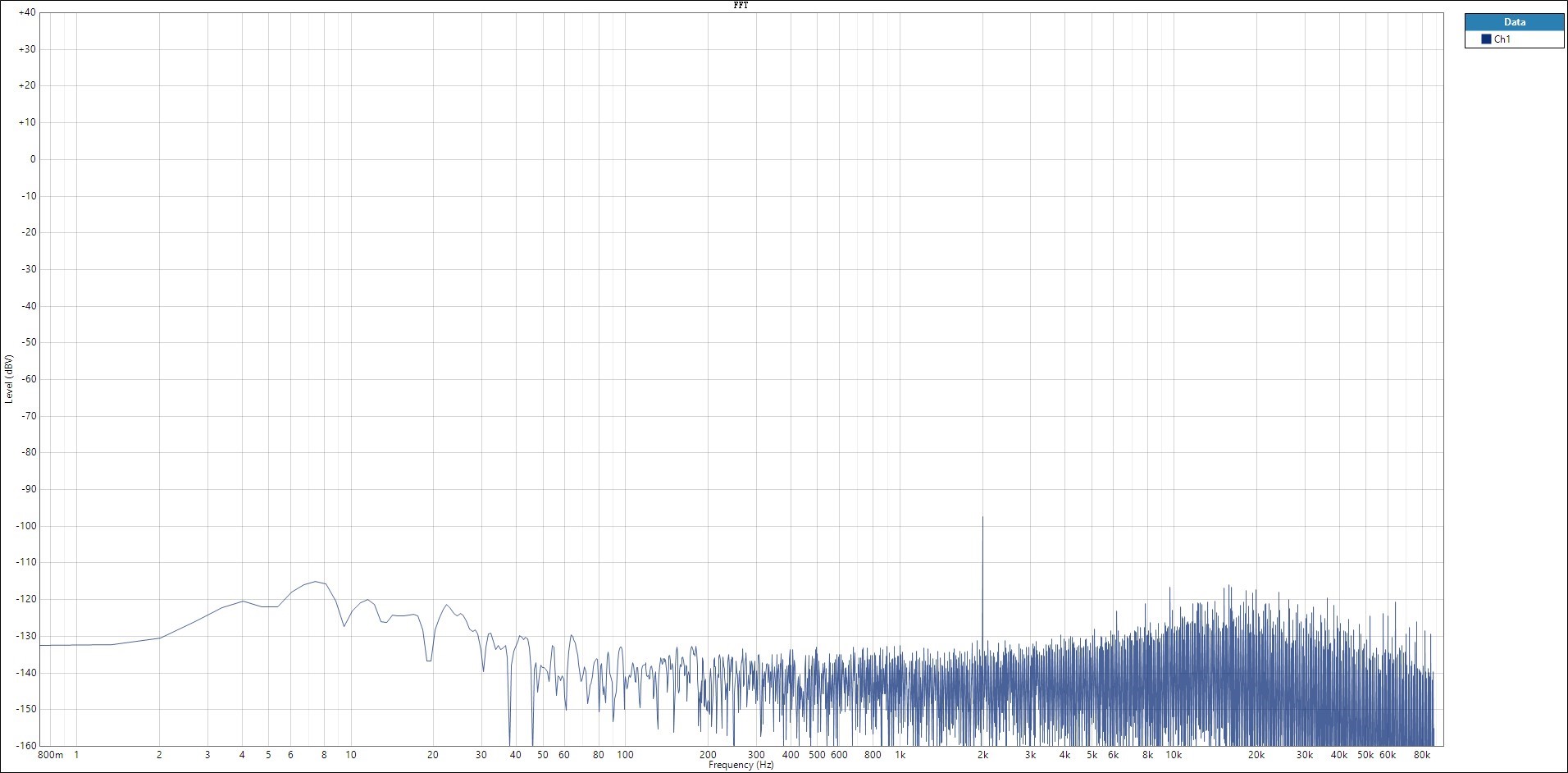

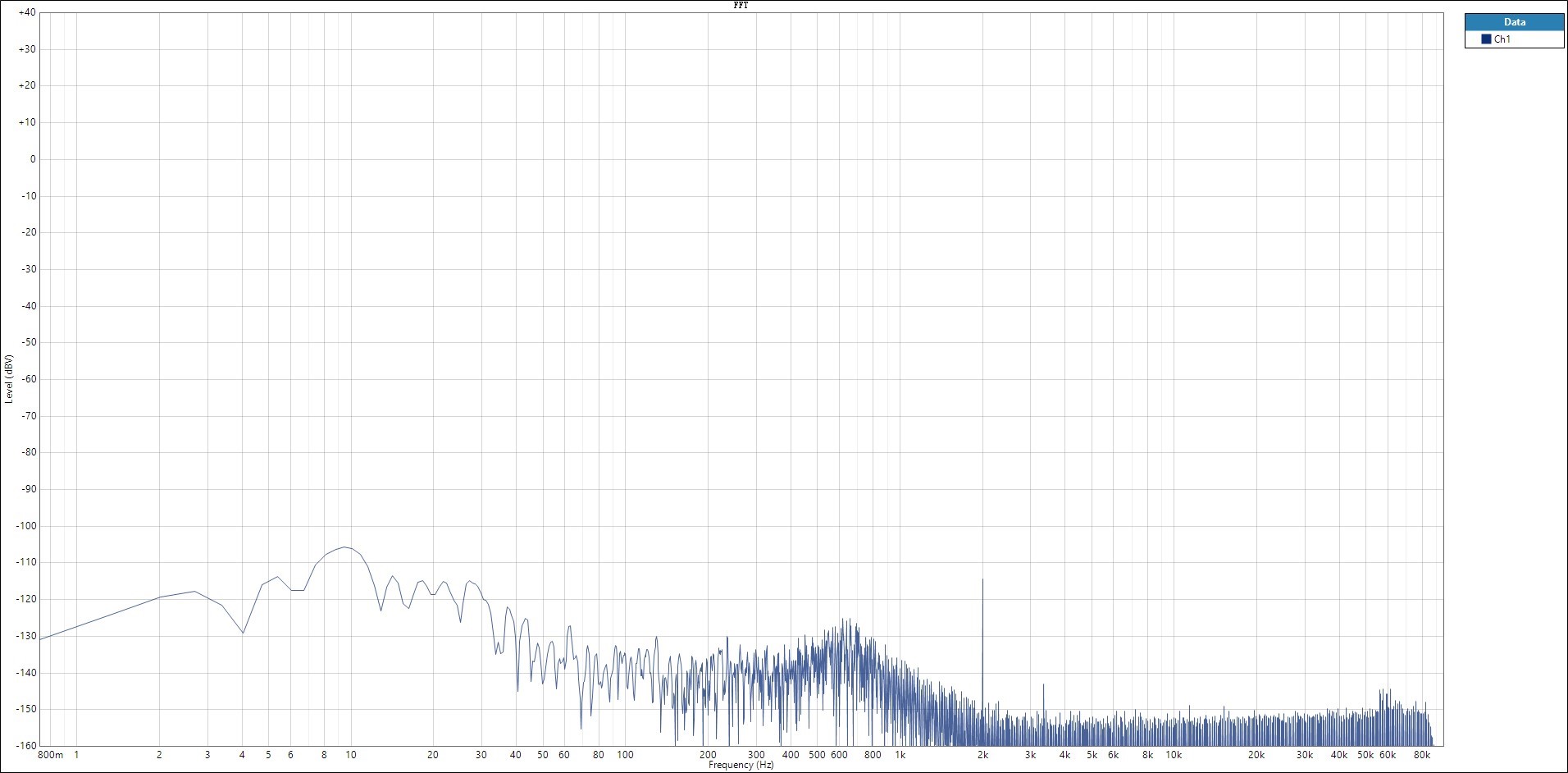

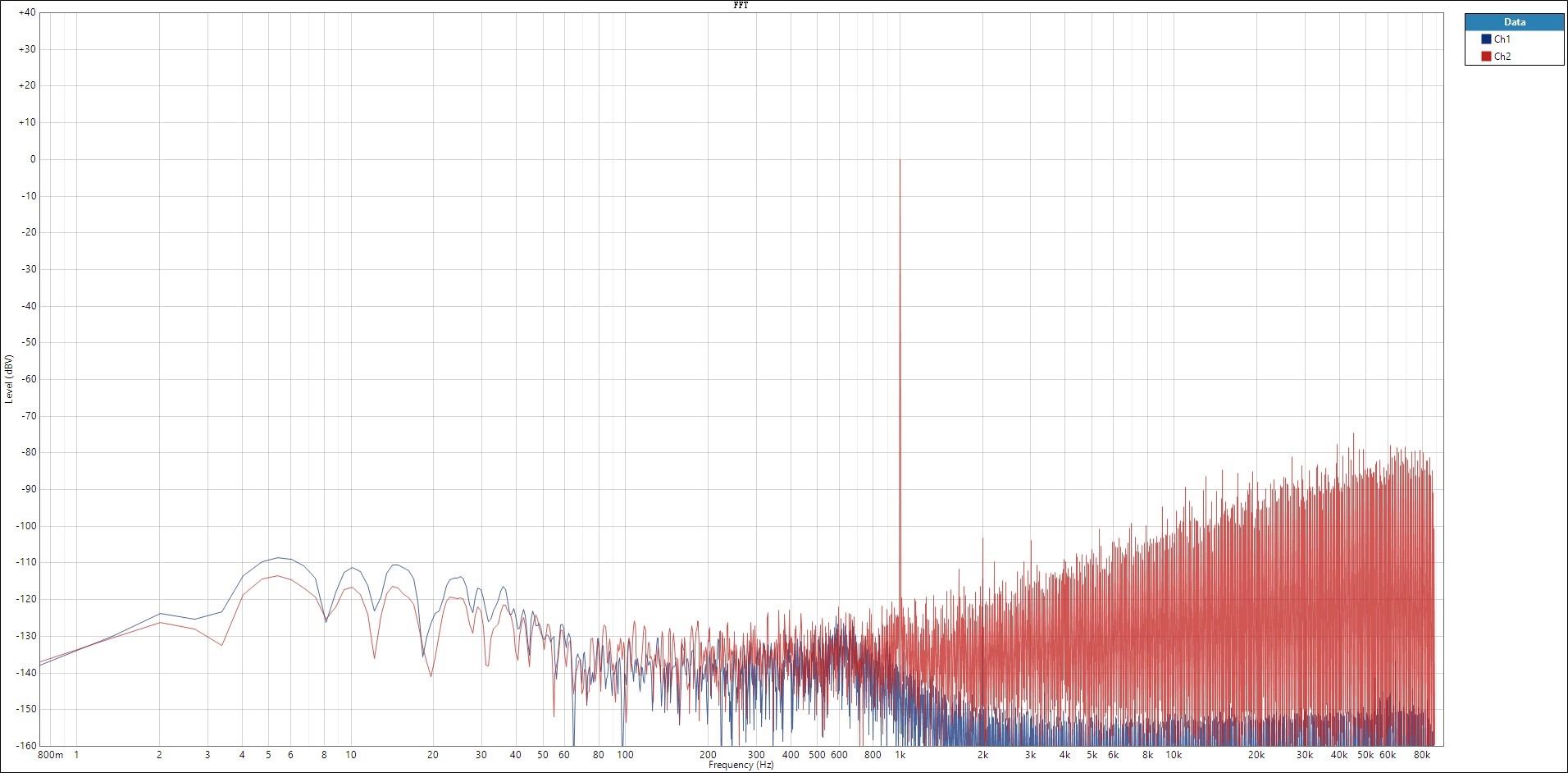

我曾经怀疑信号噪声可能与基准电压或电源的噪声有关。 所以、我尝试了在 DAC8830的 VREF 引脚上增加滤波处理。 不过、我发现即使降低了该引脚上的噪声、输出信号的噪声也没有改善、如下图所示。 在 VDD 引脚上执行了类似的测试、结果是相似的。

图:添加滤波功能之前 VREF 引脚的噪声水平

图:添加滤波功能后 VREF 引脚的噪声水平

图:VREF 管脚上的噪声优化对信号噪声没有影响

这个本底噪声水平肯定不是 DAC8830应该达到的水平。 因此、我想发表一项质询、就噪音水平下降的原因、征询意见。

此外、如果有相关的文字、我非常感谢大家的推荐。

谢谢!

Howie