主题ADC09SJ1300中讨论的其他器件

工具与软件:

专家们、您好!

我们正在开发采样板。

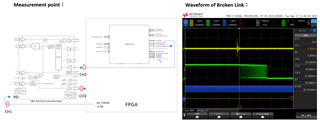

在电路板上、我们得到的 rx_lan_valid 信号将从‘1转换到‘0一次、约15分钟。

此时、出现了 IP 错误。

IP 错误为"rx_lan_invalid_somf_err_count"、"rx_lan_invalid_eomf_err_count"、"rx_lan_notintable_err_count"和"rx_lan_disp_err_count"。

您能给我一些建议、说明可能是什么原因导致了错误吗?

ADC:ADC09SJ1,300,1250Msps、JMODE11(4通道、9位、8B/10B)

TI-JESD204C IP:版本- v1.10 -最新

FPGA:xa7z030fbv484-1Q

谢谢