工具与软件:

我查看了 TI 论坛、但找不到最终的解决方案、因此发布了一个新问题。

ADS7038芯片有问题。 我似乎一次又一次地得到了错误的 ADC 值。 这在我的生产卡上发生、但我还使用与 TI ADS7038开发板通信的 NXP S32K146开发板重新创建了它。 我认为这可能是 SPI 时钟问题。

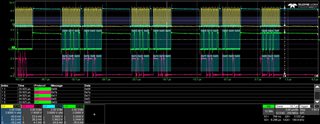

我有一些示波器 JPG 和 CSV 读数、这些读数会显示有趣/怪异的效果。 这些来自我的生产卡、但我想从 NXP/TI 的组合中获取一些迹象、以便从公式中省去我们的生产卡设计。 这需要几天时间。

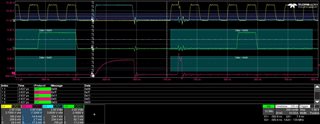

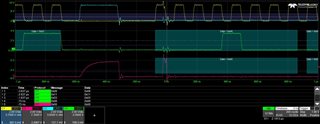

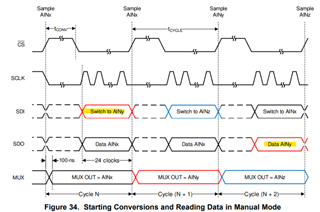

我正在从 ADC 通道3读取、并附加了通道编号、因此在从 ADC 返回的24位 MISO 中、我应该得到0xABCd00、其中0xABC 是 ADC 值、d 是通道编号(3)。

我在1Hz 和/或1KHz 下注入1V..2V 的锯齿输入。 我已将 AVDD 设置为3V。 这应该意味着我期望的值在1300..2730范围内。

我发送 WRITE CHANNEL_SEL 3、然后发送 WRITE SYSTEM_STATUS 0、并在执行第2条命令时获取 ADC 读数。 然后、我重复此序列(当前尽可能快、但以固定频率运行时也会失败-在这里发现了原始问题)。

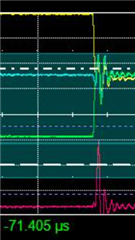

我已经修改了我的代码、如果我获得一个非3通道数或者 ADC 读数小于100或者 ADC 读数大于3700、那么我发送一个(无效的) SPI 消息0xDDEEFF 并在一个断点处停止。 当看到该0xDDEEFF 值时、我让示波器停止记录。

理想情况下、代码不应命中断点、且示波器不应停止记录。 遗憾的是、JPG 中也没有这种情况。

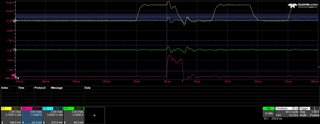

JPG、尤其是最后一个 JPG、显示 ADC 读数增加(由于锯齿输入) 0x7cc、0x7e1、0x7F1、0x000、0x80c (0x000是错误值)。

有趣的是、在0x000上、ADC 尝试驱动一个高电平位、但它持续时间不到一个时钟脉冲。

如果需要、我还在 CSV 文件中提供了4个通道(C1 = CLK、C2 = MISO、C3 = CS、C4 = MOSI)的录制文件。

当我第一次观察到这个问题时(在有示波器跟踪之前)、我认为它总是在2048 (这是4096 12位 ADC 最大范围的一半)左右发生。 在连接的 JPG 中、问题看起来像是 ADC 尝试从1 (意味着 ADC >= 2048)开始、这将支持"在 MSB=1 (ADC 大约2048)附近发生"。 然而、对0.5V..1V 范围内的锯齿(因此无法接近2048 ADC)进行进一步测试时也会出现问题。 这可能是一个因素,但不是完整的故事。

我对大多数寄存器使用默认值、具体来说、CPOL/CPHA 都为0。 通道1和3设置为模拟输入、所有其他通道均设置为 GPIO 输入。 在我使用 NXP/TI 开发板时、我将所有通道设置为0V 或3V、但通道3除外、它具有锯齿状结构。

在其他测试中、我注意到以下几点

- 错误的通道编号(通常是所需通道的两倍)、即通道6、而不是3。

- 有时、我使用的是通道0、但使用的频率要比获得所需通道的两倍还要低。

- 我还进行了一些读取、寄存器、0操作、并取回了看起来像 ADC 读数(2字节的 ADC/通道值、然后是0x00)的内容、而不是寄存器读取(1字节的寄存器值、然后是0x00 0x00)。

在读取寄存器0中、返回 ADC 读数、我猜 ADC 未正确解释命令、因此拒绝了该命令、并因此输出了最新的 ADC 读数。 如果底层问题是时钟问题、那么这是合理的、并且与我看到双倍通道数的情况相反。

你是否能够说明这个问题? JPG 和 CSV 文件是否有帮助?

谢谢

Darren

e2e.ti.com/.../Z2_2D002D00_got-you-1_2D002D00_00001.csve2e.ti.com/.../Z3_2D002D00_got-you-1_2D002D00_00001.csve2e.ti.com/.../Z4_2D002D00_got-you-1_2D002D00_00001.csve2e.ti.com/.../Z1_2D002D00_got-you-1_2D002D00_00001.csv

e2e.ti.com/.../Z2_2D002D00_got-you-1_2D002D00_00001.csve2e.ti.com/.../Z3_2D002D00_got-you-1_2D002D00_00001.csve2e.ti.com/.../Z4_2D002D00_got-you-1_2D002D00_00001.csve2e.ti.com/.../Z1_2D002D00_got-you-1_2D002D00_00001.csv